Mohammad Tehranipoor · Cliff Wang Editors

# Introduction to Hardware Security and Trust

# Introduction to Hardware Security and Trust

Mohammad Tehranipoor • Cliff Wang Editors

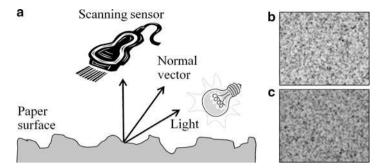

# Introduction to Hardware Security and Trust

Editors

Mohammad Tehranipoor

ECE Department

University of Connecticut

371 Fairfield Way, Unit 2157

Storrs, CT 06269

USA

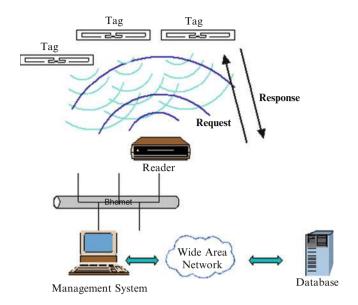

tehrani@engr.uconn.edu

Cliff Wang

Computing and Information Science

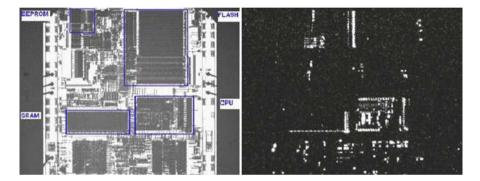

Division

US Army Research Office

PO Box 12211

Research Triangle Park

NC 27709-2211

USA

cliff.wang@us.army.mil

ISBN 978-1-4419-8079-3 e-ISBN 978-1-4419-8080-9 DOI 10.1007/978-1-4419-8080-9 Springer New York Dordrecht Heidelberg London

Library of Congress Control Number: 2011935539

### © Springer Science+Business Media, LLC 2012

All rights reserved. This work may not be translated or copied in whole or in part without the written permission of the publisher (Springer Science+Business Media, LLC, 233 Spring Street, New York, NY 10013, USA), except for brief excerpts in connection with reviews or scholarly analysis. Use in connection with any form of information storage and retrieval, electronic adaptation, computer software, or by similar or dissimilar methodology now known or hereafter developed is forbidden.

The use in this publication of trade names, trademarks, service marks, and similar terms, even if they are not identified as such, is not to be taken as an expression of opinion as to whether or not they are subject to proprietary rights.

Printed on acid-free paper

Springer is part of Springer Science+Business Media (www.springer.com)

# **Contents**

| 1  | Junxia Ma and Mohammad Tehranipoor                                                                  | 1   |

|----|-----------------------------------------------------------------------------------------------------|-----|

| 2  | <b>Hardware Implementation of Hash Functions</b> Zhijie Shi, Chujiao Ma, Jordan Cote, and Bing Wang | 27  |

| 3  | RSA: Implementation and Security                                                                    | 51  |

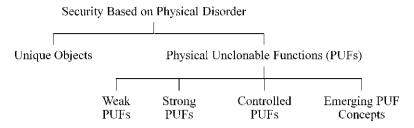

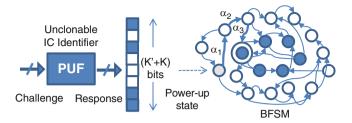

| 4  | <b>Security Based on Physical Unclonability and Disorder</b>                                        | 65  |

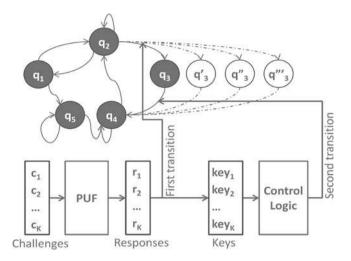

| 5  | Hardware Metering: A Survey                                                                         | 103 |

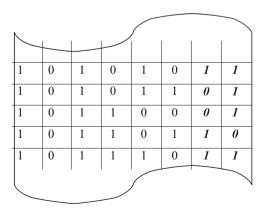

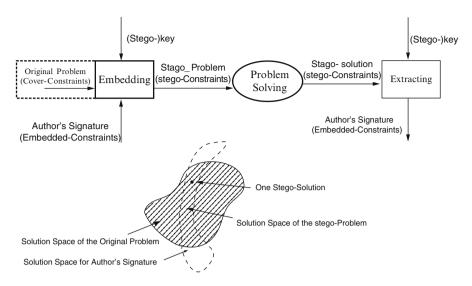

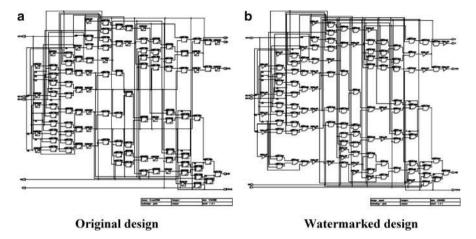

| 6  | Secure Hardware IPs by Digital Watermark                                                            | 123 |

| 7  | Physical Attacks and Tamper Resistance                                                              | 143 |

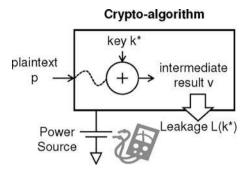

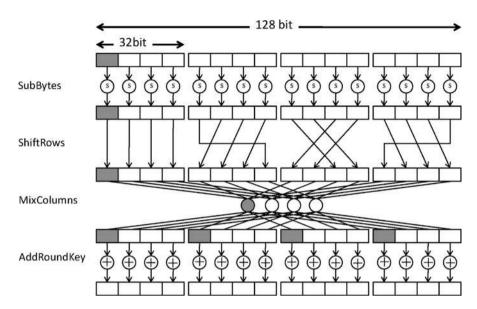

| 8  | Side Channel Attacks and Countermeasures                                                            | 175 |

| 9  | Trusted Design in FPGAs                                                                             | 195 |

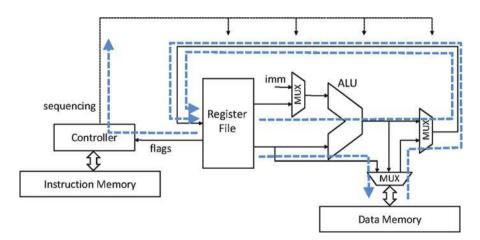

| 10 | Security in Embedded Systems  Yunsi Fei and Juan Carlos Martinez Santos                             | 231 |

| 11 | Side-Channel Attacks and Countermeasures for Embedded Microcontrollers                              | 263 |

vi Contents

| 12 | Security for RFID Tags                                                         | 283 |

|----|--------------------------------------------------------------------------------|-----|

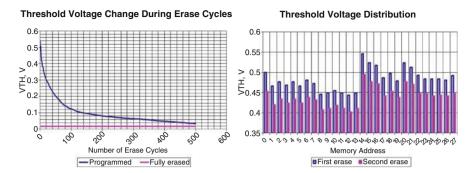

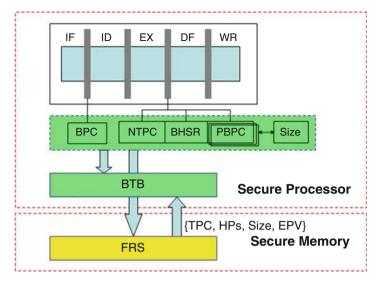

| 13 | Memory Integrity Protection  Yin Hu and Berk Sunar                             | 305 |

| 14 | <b>Trojan Taxonomy</b> Ramesh Karri, Jeyavijayan Rajendran, and Kurt Rosenfeld | 325 |

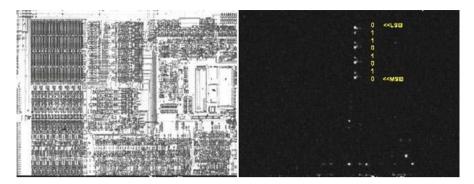

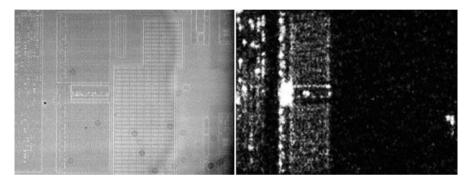

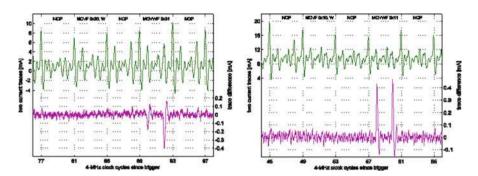

| 15 | Hardware Trojan Detection                                                      | 339 |

| 16 | <b>Design for Hardware Trust</b>                                               | 365 |

| 17 | Security and Testing                                                           | 385 |

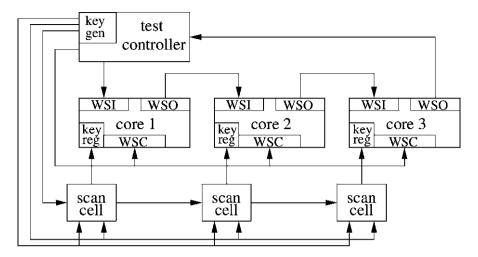

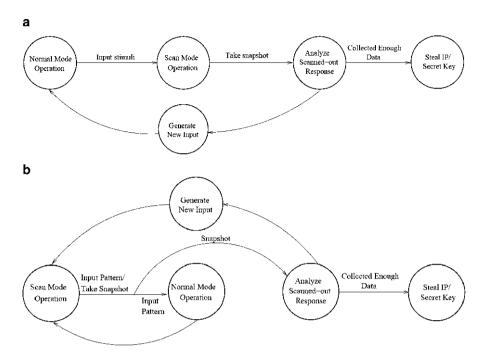

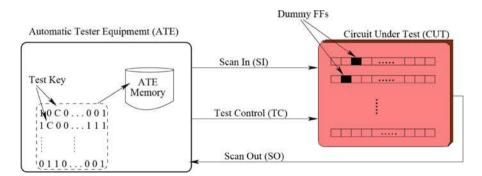

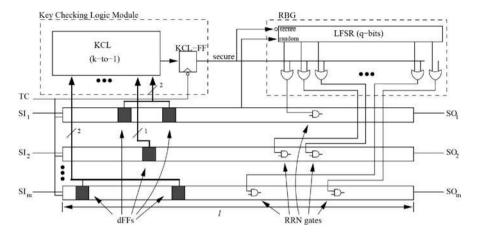

| 18 | Protecting IPs Against Scan-Based Side-Channel Attacks                         | 411 |

# **Contributors**

Swarup Bhunia Case Western Reserve University, Cleveland, Ohio, USA

Zhimin Chen ECE Department, Virginia Tech, Blacksburg, VA 24061, USA

**Jordan Cote** Computer Science and Engineering Department, University of Connecticut, Storrs, CT, USA

**Srinivas Devadas** Electrical Engineering and Computer Science, Massachusetts Institute of Technology, Cambridge, USA

**Jia Di** Computer Science and Computer Engineering Department, University of Arkansas, Fayetteville, Arkansas, USA

**Yunsi Fei** Department of Electrical and Computer Engineering, University of Connecticut, Storrs, CT, USA

**Yin Hu** Worcester Polytechnic Institute, Worcester, MA, USA

**Yier Jin** Department of Electrical Engineering, Yale University, New Haven, CT 06520, USA

Ramesh Karri Polytechnic Institute of New York University, Brooklyn, NY, USA

**Farinaz Koushanfar** Electrical and Computer Engineering Department, Rice University, Houston, Texas 77215-1892, USA

**Jeremy Lee** DFT Engineer, Texas Instruments, Dallas, TX, USA

**Eric Love** Department of Electrical Engineering, Yale University, New Haven, CT 06520, USA

**Chujiao Ma** Computer Science and Engineering Department, University of Connecticut, Storrs, CT, USA

Junxia Ma University of Connecticut, Storrs, CT, USA

**Ken Mai** Carnegie Mellon University, 5000 Forbes Avenue, Pittsburgh, PA 15213, USA

viii Contributors

**Mehrdad Majzoobi** Electrical and Computer Engineering Department, Rice University, 6100 Main, MS380, Houston, TX 77005, USA

**Yiorgos Makris** Department of Electrical Engineering, Yale University, New Haven, CT 06520, USA

**Juan Carlos Martinez Santos** Department of Electrical and Computer Engineering, University of Connecticut, Storrs, CT, USA

Currently on leave from Universidad Tecnologica de Bolivar, Cartagena, Colombia

Seetharam Narasimhan Case Western Reserve University, Cleveland, Ohio, USA

**Miodrag Potkonjak** Computer Science Department, University of California Los Angeles, Los Angeles, CA 90095-1596, USA

**Gang Qu** Electrical and Computer Engineering Department, Institution for Systems Research, University of Maryland, College Park, MD 20742, USA

**Jeyavijayan Rajendran** Polytechnic Institute of New York University, Brooklyn, NY, USA

Kurt Rosenfeld Google Inc., New York, USA

**Ulrich Rührmair** Computer Science, Technische Universitat Munchen, Munich, Germany

Patrick Schaumont ECE Department, Virginia Tech, Blacksburg, VA 24061, USA

**Zhijie Shi** Computer Science and Engineering Department, University of Connecticut, Storrs, CT, USA

**Sergei Skorobogatov** University of Cambridge, Computer Laboratory, JJ Thomson Avenue, Cambridge CB3 0FD, UK

Berk Sunar Worcester Polytechnic Institute, Worcester, MA, USA

**Mohammad Tehranipoor** UCONN Electrical and Computer Engineering, University of Connecticut, 371 Fairfield Way, Unit 2157 Storrs, CT 06269-2157, USA

**Dale R. Thompson** Computer Science and Computer Engineering Department, University of Arkansas, Fayetteville, Arkansas, USA

**Nicholas Tuzzio** UCONN Electrical and Computer Engineering, University of Connecticut, 371 Fairfield Way, Unit 2157, Storrs, CT 06269-2157, USA

**Bing Wang** Computer Science and Engineering Department, University of Connecticut, Storrs, CT, USA

Lin Yuan Synopsys Inc., Mountain View, CA 94043, USA

# **Chapter 1 Background on VLSI Testing**

Junxia Ma and Mohammad Tehranipoor

# 1.1 Introduction

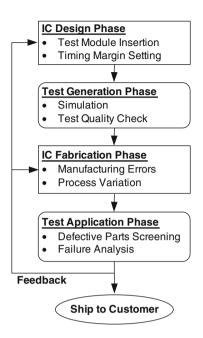

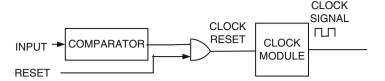

As technology feature size of devices and interconnects shrink at the rate predicted by Moore's law, gate density and design complexity on single integrated chip (IC) keep increasing in recent decades. The close to nanoscale fabrication process introduces more manufacturing errors. New failure mechanisms that are not covered by current fault models are observed in designs fabricated in new technologies and new materials. At the same time, the power and signal integrity issues that come with scaled supply voltages and higher operating frequencies increase the number of faults that violate the predefined timing margin. VLSI testing has become more and more important and challenging to verify the correctness of design and manufacturing processes. The diagram shown in Fig. 1.1 illustrates the simplified IC production flow. In the design phase, the test modules are inserted in the netlist and synthesized in the layout. Designers set timing margin carefully to account for the difference between simulation and actual operation mode, such as uncertainties introduced by process variation, temperature variation, clock jitter, etc. However, due to imperfect design and fabrication process, there are variations and defects that make the chip violate this timing margin and cause functional failure in field. Logic bugs, manufacturing error, and defective packaging process could be the source of errors. It is thus mandatory to screen out the defective parts and prevent shipping them to customers to reduce custom returns.

Nowadays, the information collected from testing is used not only to screen defective products from reaching the customers but also to provide feedback to improve the design and manufacturing process (see Fig. 1.1). In this way, VLSI testing also improves manufacturing yield level and profitability.

UCONN Electrical and Computer Engineering, University of Connecticut, Storrs, CT, USA e-mail: junxia@engr.uconn.edu; tehrani@engr.uconn.edu

J. Ma (⋈) · M. Tehranipoor

**Fig. 1.1** Simplified IC design, fabrication, and test flow

# 1.2 Test Costs and Product Quality

Although high test quality is preferred, it always comes at the price of high test cost. Trade-offs are necessary to reach the required test quality with minimum cost [1]. In this Section, concepts of test costs, VLSI yield, and product quality are introduced. These concepts, when applied in electronic test, lead to economic arguments that justify design-for-testability (DFT) [2].

# 1.2.1 Test Costs

Test cost includes the cost of automatic test equipment (ATE) (initial and running cost), the cost of test development (CAD tools, test vector generation, test programming) [3], and the cost of DFT [4]. The scan design techniques can significantly reduce the cost of test generation and the Built-in self-test (BIST) method can lower the complexity and cost of ATE [5].

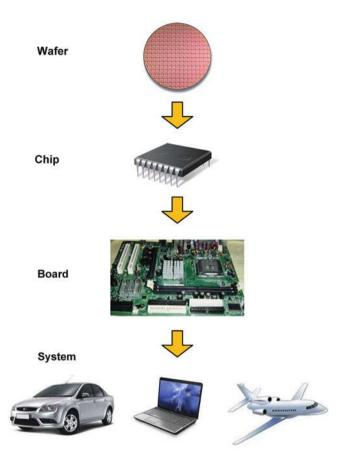

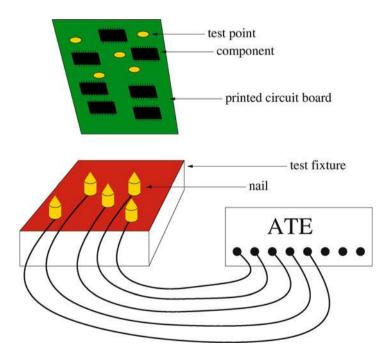

As shown in Fig. 1.2, the electronic industry tests chips in different levels. Wafer testing is performed during semiconductor device fabrication using automated test equipment (ATE). During this step, each device that is present on the wafer is tested for functional defects by applying special test patterns to it. The wafer is then cut into rectangular blocks, each of which is called a die. Each good die is then packaged, and all packaged devices are tested through final testing again

Fig. 1.2 Test levels: wafer, packaged chip, PCB, system in field

on the same or similar ATE used during wafer probing. After the chips are shipped to the customers, they will perform PCB testing and system testing again because the rule of ten holds according to experience [6]. It usually requires ten times more expensive cost than chip level to repair or replace defective ASIC at PCB level. After chips are assembled into systems, if a board fault is not caught in PCB testing, it needs ten times as much at the system level as at the board level to find the fault. Nowadays, as the systems are much more complex than year 1982 when the empirical rule was first stated in [6], the times of cost increase are much more than 10X. For airplanes, a chip fault uncaught in testing can cause thousands or millions times loss. For the same reason, VLSI testing is essential to reach "zero-defect" goal for mission critical applications.

# 1.2.2 Defect, Yield, and Defect Level

A manufacturing *defect* is a finite chip area with electrically malfunctioning circuitry caused by errors in the fabrication process. Defect on wafers could be caused by process variation, such as impurities in wafer material and chemicals, dust particles on masks or in the projection system, mask misalignment, incorrect temperature control, etc. Typical defects are broken (open) metal wires, missing contracts, bridging among metal lines, missing transistors, incorrect doping levels, void vias, resistive open vias, and many other phenomena that can cause the circuit to fail. A chip with no manufacturing defect is called a good chip. Fraction (or percentage) of good chips produced in a manufacturing process is called the *yield*. Yield is denoted by symbol Y. For chip area A, with fault density f, where f is the average number of faults per unit area, fault clustering parameter  $\beta$ , and fault coverage T, the yield equation [5] is expressed as later.

$$Y(T) = \left(1 + \frac{TAf}{\beta}\right)^{-\beta}. (1.1)$$

Assuming that tests with 100% fault coverage (T=1.0) remove all faulty chips, the yield Y(1) is:

$$Y = Y(1) = \left(1 + \frac{Af}{\beta}\right)^{-\beta}.$$

(1.2)

Good test process can reject most of the defective parts. However, even it can reject all the faulty chips, it cannot improve the process yield by itself unless the diagnostic information collected during test is feedback to the design and fabrication process. There are two ways of improving the process yield [5]:

- 1. *Diagnosis and repair*. Defective parts are diagnosed and then repaired. Although in this way the yield is improved, it increases the cost of manufacturing.

- 2. *Process diagnosis and correction*. By identifying systematic defects and their root cause, the yield can be improved once the cause is eliminated during manufacturing process. Process diagnosis is preferred method of yield improvement.

A metric used to measure the effectiveness of tests and the manufactured product quality is defect level (DL), which is defined as the ratio of faulty chips among the chips that pass tests. It is measured as parts per million (ppm). For commercial VLSI chips a DL greater than 500 ppm is considered unacceptable.

There are two methods for the determination of defect level. One is from the field return data. Chips failing in the field are returned to the manufacturer. The number of returned chips normalized to one million chips shipped is the defect level. The other way is using test data. Fault coverage of tests and chip fallout rate are analyzed. A modified yield model is fitted to the fallout data to estimate the defect level, where chip fallout is the fraction of chips failing up to a vector in the test set, which is 1-Y(T).

When chip tests have a fault coverage T, the defect level is given by the following equation [5]:

$$DL(T) = \frac{Y(T) - Y(1)}{Y(T)} = 1 - \frac{Y(1)}{Y(T)} = 1 - \left(\frac{\beta + TAf}{\beta + Af}\right)^{\beta}, \quad (1.3)$$

where Af is the average number of faults on the chip of area A and  $\beta$  is the fault clustering parameter. Af and  $\beta$  are determined by test data analysis. This equation gives DL as a fraction that should be multiplied by  $10^6$  to obtain ppm. For zero fault coverage, DL(0) = 1 - Y(1), where Y(1) is the process yield. For a 100% fault coverage, DL(1) = 0.

An alternative equation relating detects level, Yield, and fault-coverage, in case of unclustered random defects is [22]:

$$DL(T) = 1 - Y^{1-T}, (1.4)$$

where T is the fault coverage of tests and Y is the ratio of the "devices tested good" to the "total number of devices tested or fabricated/manufactured."

# 1.3 Test Generation

# 1.3.1 Structural Test vs. Functional Test

In the past, functional patterns were used to verify if there are any errors at the output. A complete functional test will check each entry of the truth table. It is possible with small input numbers. However, as the exhaustive testing of all possible input combinations grows exponentially as the number of inputs increases, such a test will be too long and impossible for real circuits with several hundred inputs. Eldred derived tests that would observe the state of internal signals at primary outputs of a large digital system in 1959 [7]. Such tests are called structural tests because they depend on the specific structural (gate type, interconnect, netlist) of the circuits [5]. Structural test has become more attractive over the last decade because of the controllable testing time.

Structural testing is considered as white-box testing because the knowledge of the internal logic of a system is used for test generation. It makes no direct attempt to determine if the overall functionality of the circuit is correct. Instead, it checks whether the circuit has been assembled correctly from low-level circuit elements as specified in the netlist. The stipulation is that if the circuit elements are confirmed to be assembled correctly then the circuit should be functioning correctly. Functional test attempts to validate that the circuit under test functions according to its functional specification. It can be viewed as black-box test. Functional automatic test-pattern generation (ATPG), (refer to 1.3.4) programs generates complete set

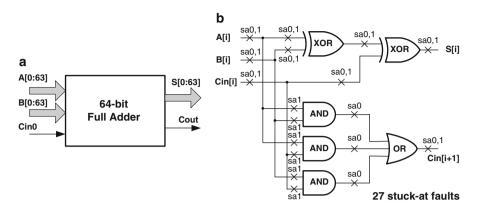

Fig. 1.3 A 64-bit ripple-carry adder: (a) functional test; (b) structural stuck-at fault test

of tests for circuit input-output combinations to completely exercise the circuit function. Figure 1.3 shows a 64-bit ripple-carry adder and the logic circuit design for one bit slice of the adder. As can be seen from Fig. 1.3a, the adder has 129 inputs and 65 outputs. Therefore, to completely test it using functional patterns, we need  $2^{129} = 6.80 \times 10^{38}$  input patterns, and to verify  $2^{65} = 3.69 \times 10^{19}$  output response. Using ATE whose operating frequency is 1 GHz, it would take  $2.15 \times 10^{22}$  years to apply all of these patterns to this adder circuit assuming that the circuit can operate at 1 GHz too. Today considering most of the circuit size much larger than this simple adder, exhaustive functional test is impractical to test them in most of the case. Nowadays small numbers of functional test patterns are found to be useful to screen sever defects. For some applications, such as microprocessors, functional testing is still a very important part. It is quite fast to apply structure test to this 64-bit adder circuit. There are totally 27 stuck-at faults for one bit adder after we discard the equivalent faults in Fig. 1.3b. For a 64-bit adder, there are  $27 \times 64 = 1,728$  faults. It needs at most 1,728 test patterns. Using 1 GHz ATE it needs only 0.000001728 s to apply these patterns. Since this pattern set covers all possible stuck-at faults in this adder, it achieves same fault coverage as the huge functional test pattern set. Thus we can see the advantage and importance of structural testing.

# 1.3.2 Fault Models

There are three terms that are usually used to describe the incorrectness of an electronic system.

• *Defect:* A defect in an electronic system is the unintended difference between the implemented hardware and its intended design. Typical defects in VLSI chips are: process defects, material defects, aging defects, and package defects.

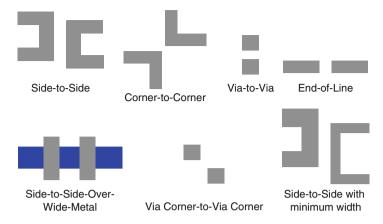

Fig. 1.4 Five Type of bridging faults [26]

- *Error:* A wrong output signal produced by a defective system is called an error. An error is an effect whose cause is some "defect."

- Fault: A representation of a "defect" at the abstracted function level is called a fault.

Fault model is a mathematical description of how a defect alters design behavior. A fault is said to be detected by a test pattern if, when applying the pattern to the design, any logic value observed at one or more of the circuit's primary outputs differs between the original design and the design with the fault. There are a lot of fault models developed to describe different kinds of physical defects. The most common fault modes for modern VLSI test includes: stuck-at fault, bridging fault, delay faults (transition delay fault and path delay fault), stuck-open and stuck-short faults, etc.

- Stuck-at faults: A signal, which is an input or an output of a logic gate or flip-flop is stuck at a 0 or 1 value, independent of the inputs to the circuit. Single stuck-at fault is widely used, i.e., two faults per line, stuck-at-1 (sa1), and stuck-at-0 (sa0). An example of stuck-at fault in the circuit is shown in Fig. 1.3.

- Bridging faults: Two signals are connected together when they should not be. Depending on the logic circuitry employed, this may result in a wired-OR or wired-AND logic function. As there are O(n²) potential bridging faults, they are normally restricted to signals that are physically adjacent in the design. Sketches of seven typical types of bridging faults are shown in Fig. 1.4. These types are derived from DRC and DFM rules and known bridge causing layout features [8]:

- Type 1: Side-to-Side

- Type 2: Corner-to-Corner

- Type 3: Via-to-Via

- Type 4: End-of-Line

- Type 5: Side-to-Side Over Wide Metal

- Type 6: Via Corner-to-Via Corner

- Type 7: Side-to-Side with Minimum Width

- Delay faults: These faults make the signal propagate slower than normal, and cause the combinational delay of a circuit to exceed clock period. Specific delay faults are: transition delay faults (TDF), path delay faults (PDF), gate delay faults, line delay faults, and segment delay faults. Among them slow-to-rise and slow-to-fall PDF and TDF are the most commonly used ones. Path delay fault model targets the cumulative delay through the entire list of gates in a path, while the transition fault model targets each gate output in the design.

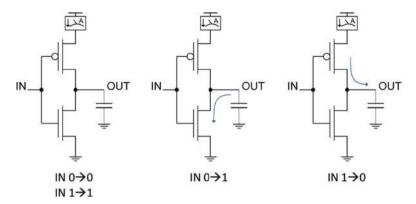

- Stuck-open and Stuck-short faults: AMOS transistor is considered as an ideal switch. Stuck-open and stuck-short faults model the switch being permanently in either the open or the shorted state. And they assume just one transistor to be stuck-open or stuck short. The effect of a stuck-open fault is a floating state at the output of the faulty logic gate. It can be detected in the similar way as detecting a stuck-at fault at the output fault on the gate's output pin. The effect of stuck-short fault is that it short-connects power line and ground line. Quiescent current (IDDQ) measurement can be used to detect such fault.

# 1.3.3 Testability: Controllability and Observability

Testability is represented by *controllability* and *observability* measures that approximately quantify how hard it is to set and observe internal signal of a circuit. Controllability is defined as the difficulty of setting a particular logic signal to a 0 or a 1. Observability is defined as the difficulty of observing the state of a logic signal. Testability analysis can be used for analysis of difficulty of testing internal circuit parts, and based on it to redesign or add special test hardware (test point) in the circuit to increase its testability. It can also be used as guidance for algorithms computing test patterns to avoid using hard-to-control lines. Test generation algorithms using heuristics usually apply some kind of testability measures to their heuristic operations, which greatly speed up the test generation process. Through testability analysis, estimation of fault coverage, number of untestable faults and test vector length is also possible.

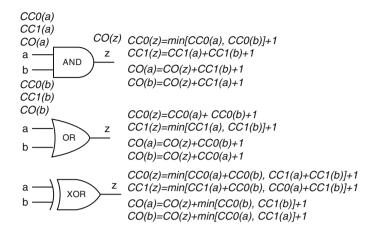

Testability analysis involves circuit topological analysis without test vectors and search algorithm. It has linear complexity. Sandia controllability observability analysis program (SCOAP) is a systematic, efficient algorithm, proposed by Goldstein [9] and widely used to compute controllability and observability measures. It consists of six numerical measures for each signal (l) in the circuit. Three combinational measures are:

• CC0(*l*): combinational 0-controllability; it represents the difficulty of setting circuit line to logic 0.

- CC1(*l*): combinational 1-controllability; it represents the difficulty of setting circuit line to logic 1.

- CO(l): combinational observability; it describes the difficulty of observing a circuit line.

Similarly, there are three sequential measures, which are SC0(l) as sequential 0-controllability, SC1(l) as sequential 1-controllability, and SO(l) as sequential observability. Generally, the three combinational measures are related to the number of signals that may be manipulated to control or observe signal l. The three sequential measures are related to the number of time-frames (or clock cycles) needed to control or observe [5]. The controllability range is between 1 to infinity  $(\infty)$  and observability range is from 0 to  $\infty$ . The higher the measure is, the more difficult it will be to control or observe that line.

According to Goldstein's method [9], the method to compute combinational and sequential measures is described as blow.

- 1. For all PIs I, set CCO(I) = CC1(I) = 1 and SCO(I) = SC1(I) = 0; For all other nodes N, set  $CCO(N) = CC1(N) = SCO(N) = SC1(N) = \infty$ .

- 2. Starting from PIs to POs, use the CC0, CC1, SC0, and SC1 equations, to map logic gate and flip-flop input controllabilities into output controllabilities. Iterate until the controllability numbers stabilize in feedback loops.

- 3. For all POs U, set CO(U)=SO(U)=0; For all other nodes N, set  $CO(N)=SO(N)=\infty$ . Working from POs to PIs, use the CO and SO equations and the precomputed controllabilities to map output node observabilities of gates and flip-flops into input observabilities. For fanout stems Z with branches with branches Z1, ..., ZN,  $SO(Z)=\min(SO(Z1), ..., SO(ZN))$  and  $CO(Z)=\min(CO(Z1), ..., CO(ZN))$ .

- 4. If any node remains with  $CC0/SC0=\infty$  then that node is 0-uncontrollable. If any node remains with  $CC1/SC1=\infty$  then that node is 1-uncontrollable. If any node remains with  $CO=\infty$  or  $SO=\infty$  then that node is unobservable. These are sufficient but not necessary conditions.

For the computation of controllability for single logic gate, if a logic gate output is produced by setting only one input to a controlling value then

output controllability =

$$\min$$

(input controllabilites) + 1. (1.5)

If a logic gate output can only be produced by setting all inputs to noncontrolling value, then

output controllability =

$$\sum$$

(input controllabilites) + 1. (1.6)

If an output can be controlled by multiple input sets, such as XOR gate, then

output conrollability =

$$min$$

(controllabilities of input sets) + 1. (1.7)

Fig. 1.5 SCOAP controllability and observability calculation

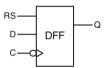

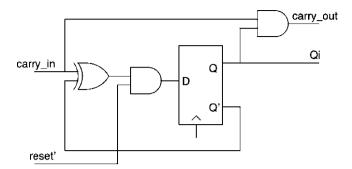

**Fig. 1.6** Resettable, negative-edge-trigged D flip-flop

For a logic gate with an input signal that needs to be observed,

input observaility = output observability

$$+\sum$$

(controllabilities of setting all other pins to non-controlling value)  $+1$ . (1.8)

Figure 1.5 presents examples of SCOAP controllability and observability calculation using AND, OR, and XOR gates.

Figure 1.6 shows a resettable negative-edge triggered D flip-flop (DFF). The combinational controllabilities CC1 or CC0 measures how many lines in the circuit must be set to make DFF output signal Q as 1 or 0, whereas sequential controllabilities SC1 or SC0 measures how many times flip-flops in the circuit must be clocked to set Q to 1 or 0. To control Q line to 1, one must to set input D to 1 and forcing a falling clock edge on C. And the reset signal line RS needs to keep as 0. Note that one needs to add 1 for the sequential measures when signals propagate from flip-flop inputs to output. Thus, CC1Q and SC1(Q) are calculated in the following way:

$$CC1(Q) = CC1(D) + CC1(C) + CC0(C) + CC0(RS)$$

$$SC1(Q) = SC1(D) + SC1(C) + SC0(C) + SC0(RS) + 1$$

(1.8)

There are two ways to set Q to 0, either through setting reset signal RS while holding clock C at 0 or clock a 0 through input D. Thus, CC0Q and SC0(Q) are calculated using the following equations:

$$CC0(Q) = \min[CC1(RS) + CC0(C), \quad CC0(D) + CC1(C) + CC0(C) + CC0(RS)]$$

$$SC0(Q) = \min[SC1(RS) + SC0(C), \quad SC0(D) + SC1(C) + SC0(C) + SC0(RS)] + 1$$

(1.9)

The input D can be observed at Q by holding RS low and generating a falling edge on the clock line C:

$$CO(D) = CO(Q) + CC1(C) + CC0(C) + CC0(RS)$$

$SO(D) = SO(Q) + SC1(C) + SC0(C) + SC0(RS) + 1$  (1.10)

RS can be observed by setting Q to a 1 and using RS:

$$CO(RS) = CO(Q) + CC1(Q) + CC0(C) + CC1(RS)$$

$SO(RS) = SO(Q) + SC1(Q) + SC0(C) + SC1(RS) + 1 + 1$  (1.11)

There are two ways to indirectly observe the clock line C: (1) set Q to 1 and clock in a 0 from D, or (2) reset the flip-flop and clock in a 1 from D. Thus,

$$\begin{split} CO(C) &= \min \left[ CO(Q) + CC0(RS) + CC1(C) + CC0(C) + CC0(D) + CC1(Q), \\ &\quad CO(Q) + CC1(RS) + CC1(C) + CC0(C) + CC1(D) \right] \\ SO(C) &= \min \left[ SO(Q) + SC0(RS) + SC1(C) + SC0(C) + SC0(D) + SC1(Q), \\ &\quad SO(Q) + SC1(RS) + SC1(C) + SC0(C) + SC1(D) \right] + 1 \end{split} \tag{1.12}$$

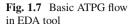

# 1.3.4 Automatic Test-Pattern Generation

ATPG is an electronic design automation (EDA) method/technology used to find an input (or test) sequence that, when applied to a digital circuit, enables testers to distinguish between the correct circuit behavior and the faulty circuit behavior caused by defects. These algorithms usually operate with a fault generator program, which creates the minimal collapsed fault list so that the designer needs not to be concerned with fault generation [5]. Controllability and observability measures are used in all major ATPG algorithms. The effectiveness of ATPG is measured by the amount of modeled defects, or fault models, that are detected and the number of generated patterns. These metrics generally indicate test quality (higher with

more fault detections) and test application time (higher with more patterns). ATPG efficiency is another important consideration. It is influenced by the fault model under consideration, the type of circuit under test (full scan, synchronous sequential, or asynchronous sequential), the level of abstraction used to represent the circuit under test (gate, register-transistor, switch), and the required test quality [10].

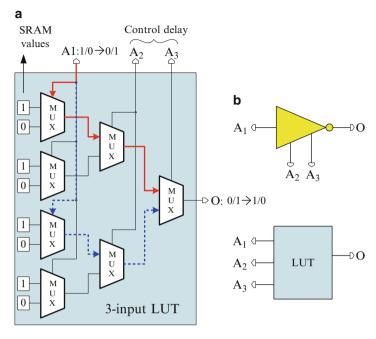

Today, because of the circuits' size and time-to-market requirement, all the ATPG Algorithms are performed by EDA tools. Figure 1.7 illustrates the basic ATPG running flow in EDA tool. The tool first reads in the design netlist and library models, then after building the model, it checks test design rules that are specified in the test protocol file. If any violations happen in this step, the tool reports the violations rule as warning or errors depending on the severity. Using the ATPG constraints specified by the users, the tool performs ATPG analysis and generates test pattern set. If the test coverage meets the users' needs, test patterns will be saved in files with specified format. Otherwise the users can modify the ATPG settings and constrains and rerun ATPG.

To be noted, there are two metrics about coverage: *test coverage* and *fault coverage*. Test coverage is the percentage of detected faults among those detectable and gives the most meaningful measure of test pattern quality. Fault Coverage is the

percent detected of all faults. It gives no credit for undetectable faults. Usually, test coverage is used as a measure for the effectiveness of the test patterns generated by the ATPG tool.

# 1.4 Structured DFT Techniques Overview

# 1.4.1 Design for Testability

DFT techniques are widely used in nowadays integrated circuits. "DFT" is a general term applied to design methods that lead to more thorough and less costly testing. In general, DFT is achieved by employing extra hardware circuits for test purpose. The extra test circuits provide improved access to internal circuit elements. Through these test circuits, the local internal state can be controlled and/or observed more easily. It adds more controllability and observability to the internal circuits. DFT plays an important role in the development of test programs and as an interface for test application and diagnostics. With appropriate DFT rules implemented, many benefits ensue from designing a system so that failures are easy to detect and locate. DFT can bring the many benefits. Generally, integrating DFT in the development cycle can help:

- Improve fault coverage

- · Reduce test generation time

- Potentially shorten test length and reduce test memory

- Reduce test application time

- Support hierarchical test

- Realize concurrent engineering

- Reduce life-cycle costs

These benefits come at the price of extra cost from pin over-ahead, more area and thus low yield, performance degradation and longer design time. However, as it reduces the overall costs of the chip, DFT is a cost-effective methodology and widely used in IC industry.

Three types of components need test in electronic systems: digital logic, memory blocks, and analog or mix-signal circuits. There are specific DFT methods for each type of components. DFT methods for digital circuits include: Ad-hoc methods and structured methods. Ad-hoc DFT method relies on good design experience and experienced designers to find the problem area. Circuit modification or test points insertion is required to improve the testability for these areas. The Ad-hoc DFT techniques are usually too labor-intensive and do not guarantee good results from ATPG. For these reasons, for large circuits it is discouraged to use Ad-hoc DFT. The common structured methods include: scan, partial scan, BIST, and boundary scan. Among them, BIST is also used for memory blocks testing. In the following, we will give a short introduction for each of these structured DFT techniques.

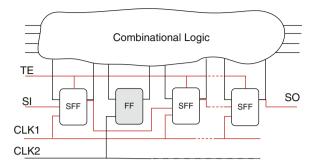

Fig. 1.9 Level-sensitive scan design (LSSD) cell

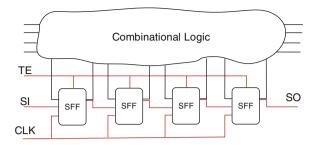

# 1.4.2 Scan Design: Scan Cell, Scan Chain, and Scan Test Compression

Scan is the most popular DFT technique. Scan design offers simple read/write access to all or subset of storage elements in a design. It also enables direct control of storage elements to an arbitrary value (0 or 1) and direct observation of the state of storage elements and hence the internal state of the circuit. In short, it gives the circuit enhanced controllability and observability.

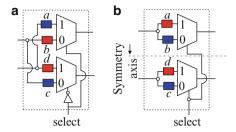

### 1.4.2.1 Scan Cell

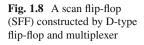

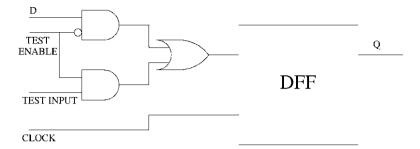

Scan design is realized by replacing flip-flops by scan flip-flops (SFFs) and connecting them to form one or more shift registers in the test mode. Figure 1.8 illustrates a SFF designed based on D-type flip-flop (DFF). A multiplexer is added in front of the DFF to construct a scan D-type flip-flop (SDFF). The test enable (TE) signal controls the working mode of the SDFF. When it is high, it selects the test mode and the scan-in (SI) bits are taken as the input of the DFF. When the TE signal is low, the SDFF works as in functional mode. It acts as a normal DFF and takes value D from the combination circuits as the input to the DFF.

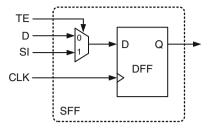

SDFF is generally used for clock edge-trigged scan design, while level-sensitive scan design (LSSD) cell is used for level-sensitive, latch-based designs. Figure 1.9 a shows a polarity-hold shift register latch design [11] that can be used as an LSSD

**Fig. 1.10** Scan chain in a sequential circuit design

scan cell. The scan cell consists of two latches, a master two-port D-latch L1 and a slave D-latch L2. D is the normal data line and CK is the normal clock line. Line +L1 is the normal output. Lines SI, A, B, and L2 form the shift portion of the latch. SI is the shift data in and +L2 is the shift data out. A and B are the two phase, non overlapping shift clocks. The major advantage of using an LSSD scan cell is that it can be used for latch-based design. In addition, it avoids performance degradation introduced by the MUX in shift-register modification. As LSSD scan cells are level-sensitive, designs using LSSD are guaranteed to be race-free. However, this technique requires routing for the additional clocks, which increases routing complexity. It can only be used for slow test application. Normal-speed testing is impossible.

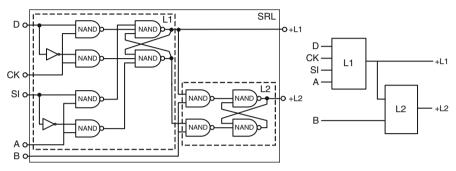

### 1.4.2.2 Scan Chain

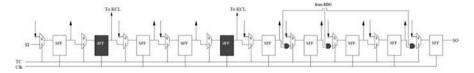

Figure 1.10 shows a scan chain in a sequential circuit design. The SFFs are stitched together and consist of a scan chain. When test enable signal TE is high, the circuit works in test (shift) mode. The inputs from scan-in (SI) are shifted through the scan chain; the scan chain states can be shifted out through scan chain and observed at the scan-out (SO) pin. The test program compares the SO values with expected values to verify the chips performance.

Multiple scan chains are usually used to reduce the time to load and observe. SFFs can be distributed among any number of scan chains, each having a separate scan-in (SI) and scan-out pin. The integrity of scan chains must be tested prior to application of scan test sequences. A shift sequence 00110011... of length n+4 in scan mode (TC=0) produces 00, 01, 11, and 10 transitions in all flip-flops and observes the result at scan chain output SO, where n is the number of SFFs in the longest scan chain.

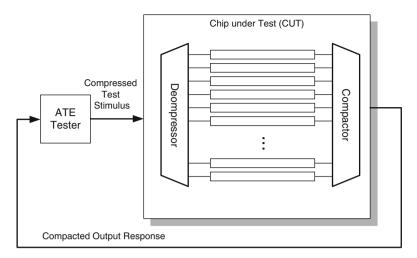

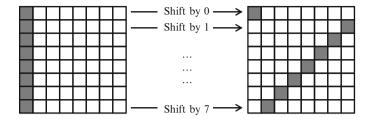

# 1.4.2.3 Scan Test Compression

As chips becomes bigger and more complex, the growing test-data volume causes a significant increase in test cost because of much longer test time and large testermemory requirements. For a scan-based test, the test data volume is proportional to

Fig. 1.11 Scan test compress

the number of test cycles. While number of test cycles and test time are related to the number of scan cells, scan chains, and scan patterns as shown in the equations later. Although theoretically increasing shift frequency reduces test time, in practice shift frequency cannot be increased too much due to power dissipation and design constraints

$$Test Cycles \approx \frac{Scan Cells \times Scan Patterns}{Scan Chains}$$

$$Test Time \approx \frac{Scan Cells \times Scan Patterns}{Scan Chains \times Shift Frequency}.$$

(1.9)

As manufacturing test cost depends very strongly on the volume of test data and test time, one of the key requirements is to reduce them dramatically. Test Compression was developed to help address this problem.

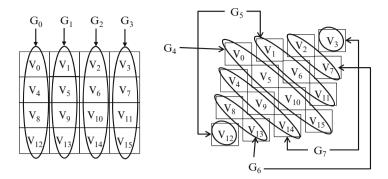

There are large portion of don't-care bits left when an ATPG tool generates a test for a set of faults. Test compression takes advantage of the small number of significant values to reduce test data and test time. Generally, the idea is to modify the design to increase the number of internal scan chains and shorten maximum scan chain lengths. As illustrated in Fig. 1.11, these chains are then driven by an on-chip decompressor, usually designed to allow continuous flow decompression where the internal scan chains are loaded as the data is delivered to the decompressor [12]. Many different decompression methods can be used [13]. One common choice is a linear finite state machine, where the compressed stimuli are computed by solving linear equations. For industrial circuits with test vectors care-bits ratio ranging from 3% to 0.2%, the test compression based on this method often results in compression ratios of 30–500 times [12].

Fig. 1.12 Partial Scan design

A compactor is required to compact all the internal scan chain outputs to the output pins. As can be seen from Fig. 1.11, it is inserted between the internal scan chain outputs and the tester scan channel outputs. The compactor must be synchronized with the date decompressor, and must be capable of handling unknown (X) states, which may come from false and multicycle paths, or other unexpected reasons.

# 1.4.3 Partial-Scan Design

While full scan designs replace all flip-flops with SFFs, partial scan design only select a subset of flip-flops to be scanned, which provides a wide spectrum of design solutions that trade off testability for the overheads (i.e., area, power overheads) incurred by scan design.

Figure 1.12 illustrates the concept of partial scan. Being different from the full-scan design shown in Fig. 1.10, not all the flip-flops are SFFs. Two separate clocks are used for scan operation and functional operation.

Selection of flip-flops that can provide the best improvements in testability is a critical part of the partial scan design process. Most SFF selection methods are based on one or several of the following techniques: testability analysis, structural analysis, and test generation [14]. Testability-based methods analyze the testability of the circuit using SCOAP measures and improve the testability by partial scan. However, for circuits with complex structure, the fault coverage achieved may not be adequate using these techniques. Partial scan selection by structural analysis targets to remove all feedback loops from a circuit, and thus simplify the circuit structure for the test generation algorithm. The problem for such techniques is, for many circuits, it may be infeasible or unnecessary to break all feedback loops to achieve desirable fault coverage. Test generation-based methods exploit information from the test generator to drive the scan selection process. The main advantage of using test generation-based techniques is that it is possible to target specific fault detection objectives rather than simplify the circuit or improve testability of specific regions in the circuit. However, it typically results in expensive computational and storage requirements [14].

As a separate clock is used for the scan operation, the states of the non-SFFs can be frozen during the scan operation and any state can be scanned into the scan register without affecting the states of the non-SFFs. In this way, test vectors can be efficiently generated by a sequential circuit test generator. However, it poses problem in the need for multiple clock trees and tight constraint on clock skew when routing of clock signals.

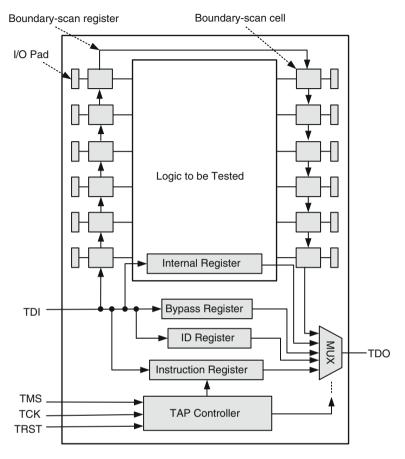

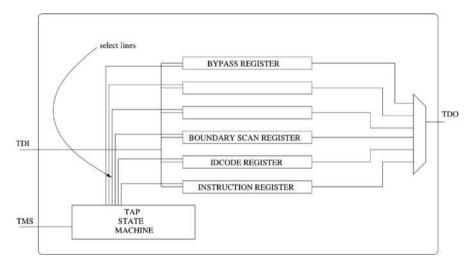

# 1.4.4 Boundary Scan

The boundary-scan technique uses a shift-register stage to test interconnects and clusters of logic, memories, etc. The boundary-scan register consists of boundary-scan cells which are inserted adjacent to each component pin so that signals at component boundaries can be controlled and observed using scan testing principles. The boundary scan controller has also emerged as the standard mechanism on SoC designs for initiating and controlling the multiple internal memory BIST controllers. Boundary scan is now a well-known and documented IEEE standard, and some test software vendors offer automated solutions. IEEE 1149.1, also known as JTAG or boundary scan, was introduced in 1990 [15]. This standard endeavors to solve test and diagnostic problems arising from loss of physical access caused by the increasing use of high pin count and BGA devices, multilayer PCBs, and densely packed circuit board assemblies. The standard outlines predefined protocols for testing and diagnosing manufacturing faults. It also provides a means for on-board programming of nonvolatile memory devices such as Flash, or in-system programming of devices like PLDs and CPLDs.

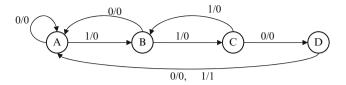

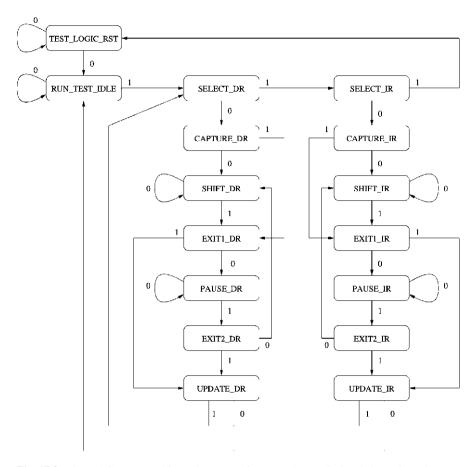

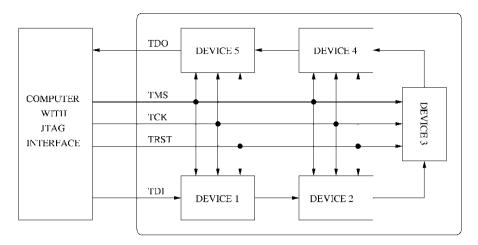

Figure 1.13 illustrates the essential boundary-scan architecture. The block of logic circuits to be tested is connected to multiple boundary-scan cells. The cells are created along with the IC circuitry when the chip is fabricated. Each cell can monitor or stimulate one point in the circuitry. The cells are then linked serially to form a long shift register whose serial input, designated Test Data Input, and serial-output ports Test Data Output become the basic I/O of a JTAG interface. The shift register is clocked through external clock signal (TCK). In addition to the serial-in, serial-out, and clock signals, a Test Mode Select (TMS) input is provided as well as an optional Test Reset pin (TRST). The TMS, TCK, and TRST signals are applied to a finite state machine called the test access port controller. Along with external binary instructions, it controls all of the possible boundary-scan functions. To stimulate the circuit, test bits are shifted in. This is called a test vector.

The primary advantage of boundary-scan technology is the ability to observe and control data independently of the application logic. It also reduces the number of overall test points required for device access, which can help lower board fabrication costs and increase package density. Simple tests using boundary scan on testers can find manufacturing defects, such as unconnected pins, a missing device, and even a failed or dead device. In addition, boundary scan provides better diagnostics. With boundary scan, the boundary-scan cells observe device

Fig. 1.13 Boundary scan architecture

responses by monitoring the input pins of the device. This enables easy isolation of various classes of test failures. Boundary scan can be used for functional testing and debugging at various levels, from IC tests to board-level tests. The technology is even useful for hardware/software integration testing and provides system level debug capability [16].

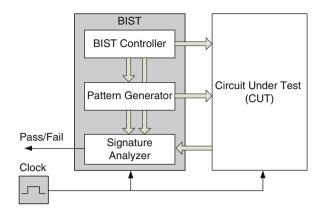

# 1.4.5 BIST Methods

Built-in Self Test, or BIST, is a DFT methodology of inserting additional hardware and software features into integrated circuits to allow them to perform self-testing, thereby reducing dependence on an external ATE and thus reducing testing cost. The concept of BIST is applicable to about any kind of circuit. BIST is also the solution

**Fig. 1.14** Build-in self-test architecture

to the testing of circuits that have no direct connections to external pins, such as embedded memories used internally by the devices. Figure 1.14 shows BIST architecture. In BIST, a test pattern generator generates test patterns and a signature analyzer (SA) compares test responses. The entire process is controlled by BIST controller.

The most two common classification of BIST are the Logic BIST (LBIST) and the Memory BIST (MBIST). LBIST, which is designed for testing random logic, typically employs a pseudo-random pattern generator to generate input patterns that are applied to the device's internal scan chain, and a multiple input signature register (MISR) for obtaining the response of the device to these test input patterns. An incorrect MISR output indicates a defect in the device. MBIST is used specifically for testing memories. It typically consists of test circuits that apply a collection of write-read-write sequences for memories. Complex write-read sequences are called algorithms, such as MarchC, Walking 1/0, GalPat, and Butterfly. The cost and benefit models for MBIST and LBIST are presented in [17]. It analyzes the economics effects of BIST for logic and memory cores.

Advantages of implementing BIST include:

- Low test cost, as it reduces or eliminates the need for external electrical testing using an ATE

- · Improved testability and fault coverage

- Support of concurrent testing

- Shorter test time if the BIST can be designed to test more structures in parallel

- At-speed testing

Disadvantages of implementing BIST include:

- Silicon area, pin counts and power overhead for the BIST circuits

- Performance degradation and timing issues

- Possible issues with the correctness of BIST results, as the on-chip testing hardware itself can fail

# 1.5 At-Speed Delay Test

At-speed delay test is widely used to test timing-related failures. It has become a common practice for nowadays semiconductor industry to include it in its test flow. In this Section, we will briefly introduce the basics of at-speed delay test, including its application, fault models used, test clock configuration, and some challenging issues when applying delay test on nanometer designs.

# 1.5.1 Why At-Speed Delay Test?

As technology scales, feature size of devices and interconnects shrink and silicon chip behavior becomes more sensitive to on-chip noise, process and environmental variations, and uncertainties. The defect spectrum now includes more problems such as high-impedance shorts, in-line resistance, power supply noises and crosstalk between signals, which are not always detected with the traditional stuck-at fault model. The number of defects that cause timing failure (setup/hold time violation) is on the rise. This leads to increased yield loss and escape and reduced reliability. Thus structured delay test, using transition delay fault model and path delay fault model, are widely adopted because of their low implementation cost and high test coverage. Transition fault testing models delay defects as large gate delay faults for detecting timing-related defects. These faults can affect the circuit's performance through any sensitized path passing through the fault site. However, there are many paths passing through the fault site; and TDF are usually detected through the short paths. Small delay defects can only be detected through long paths. Therefore, path delay fault testing for a number of selected critical (long) paths is becoming necessary. In addition, small delay defects may escape when testing speed is slower than functional speed. Therefore at-speed test is preferred to increase the realistic delay fault coverage. In [18], it is reported that the defects per million rates are reduced by 30–70% when at-speed testing is added to the traditional stuck-at tests.

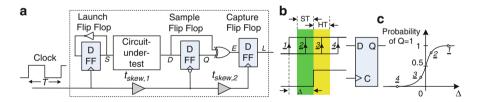

# 1.5.2 Basics on At-Speed Test: Launch-off-Capture and Launch-off-Shift

The transition fault and path delay fault are the two most widely used fault models for at-speed delay test. Path delay model targets the cumulative delay through the entire list of gates in a predefined path while the transition fault model targets each gate output in the design for a slow-to-rise and slow-to-fall delay fault [5]. The transition fault model is more widely used than path delay because it tests for at-speed failures at all nets in the design and the total fault list is equal to twice the number of nets. On the other hand, there are billions of paths in a modern design to

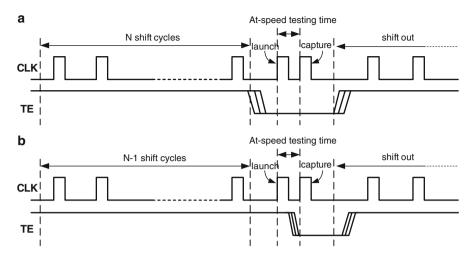

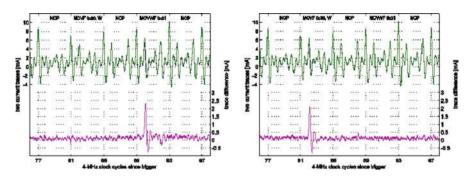

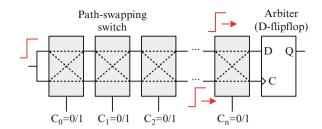

Fig. 1.15 Clock and Test Enable waveforms for LOC and LOS Tests

be tested for path delay fault leading to high analysis effort. This makes path delay fault model very cost intensive compared to transition fault model.

Compared to static testing with the stuck-at fault model, testing logic at-speed requires a test pattern with two vectors. The first vector launches a logic transition value along a path, and the second part captures the response at a specified time determined by the system clock speed. If the captured response indicates that the logic involved did not transition as expected during the cycle time, the path fails the test and is considered to contain a defect.

Scan based at-speed delay testing is implemented using launch-off-capture (LOC) (also referred as broadside [19]) and Launch-off-shift (LOS) delay tests. LOS tests are generally more effective, achieving higher fault coverage with significantly fewer test vectors, but require a fast scan enable, which is not supported by most designs. For this reason, LOC-based delay test is more attractive and used by more industry designs. Figure 1.15 shows the clock and test enable waveforms for LOC and LOS at-speed delay tests. From this figure, we can see LOS has a high requirement on the TE signal timing. An at-speed test clock is required to deliver timing for at-speed tests. There are two main sources for the at-speed test clocks. One is the external ATE and the other is on-chip clocks. As the clocking speed and accuracy requirements rise, since the complexity and cost of the tester increase, more and more designs include a phase-locked loop or other on-chip clock generating circuitry to supply internal clock source. Using these functional clocks for test purposes can provide several advantages over using the ATE clocks. First, test timing is more accurate when the test clocks exactly match the functional clocks. Secondly, the high-speed on-chip clocks reduce the ATE requirements, enabling use of a less expensive tester [18].

Fig. 1.16 At nanometer process nodes, parasitic effects increase [20]

# 1.5.3 At-Speed Delay Test Challenges

As circuit complexity and functional frequency increase, power integrity and timing integrity are becoming more and more important to circuit design and test. The test power consumption, supply voltage noise, crosstalk noise caused by signal coupling effect, and hot spots caused by nonuniform on-chip temperature will significantly impact yield and reliability. As shown in Fig. 1.16 from [20], with technology node shrinks, the percentage of delay caused by coupling effect between signal lines (crosstalk noise) and IR-drop on power and ground lines (power supply noise) is taking a larger portion. Power supply noise and crosstalk noise are becoming two important noises that impact circuits' timing integrity. The lower supply rails in today's ICs mean much less immunity from signal-integrity problems that tie directly into power integrity [21]. Supply voltages on many high-end ICs are now down to 1 V and below, leading to decreasing margins for voltage fluctuation. Simultaneous switching noise can cause ground to fluctuate, leading to difficult-to-isolate signal-integrity problems and timing issues. Power, timing, and signal integrity (SI) effects are all interdependent at 90-nm and below.

Timing failures are often the result of a combination of weak points in a design and silicon abnormalities, which reduce the noise immunity of the design and expose it to SI issues. For example, a poor power planning or missing power vias can incur on-chip power droop for some test vectors. The power droop can impact a gate(s) on a critical path and it may cause timing failure. This failure may only be excited with certain test vectors as inputs. If the corresponding test vector is not included in the test pattern set, the failure becomes an escape and cannot be reproduced during diagnosis with the current test pattern set. Current automatic test pattern

generation (ATPG) tools are not aware of the switching distribution on the layout and the pattern induced noises. There are escapes and "No Problem Found" parts returned by customers, which have passed the tests using the layout-unaware test patterns generated by ATPG tools. Thus, high-quality test patterns are imperative which can be used to capture noise-induced delay problems during production test and identify noise-related failures during diagnosis [23–25].

# References

- Druckerman H, Kusco M, Peteras S, and Shephard P III (1993) Cost trade-offs of various design for test techniques. Proc Econo Des Test Manuf, pp 45–50

- 2. Agrawal VD (1994) A tale of two designs: the cheapest and the most economic. J Electron Test 2–3(5): 131–135

- Dear ID, Dislis C, Ambler AP, Dick JH (1991) Economic effects in design and test. IEEE Design Test Comput 8(4): 64–77

- Pittman JS, Bruce WC (1984) Test logic economic considerations in a commercial VLSI chip environment. In: Proceedings of the International Test Conference, October 1984, pp 31–39

- Bushnell ML, Agrawal VD (2000) Essentials of Electronic Testing for Digital, Memory, and Mixed-signal VLSI Circuits. Kluwer Academic Publishers, Dordrecht (Hingham, MA)

- 6. Davis B (1982) The Economics of Automatic Testing. McGraw-Hill, London, United Kingdom

- 7. Eldred RD (1959) Test routines based on symbolic logical statements. J ACM 6(1): 33-36

- 8. Keim M, Tamarapalli N, Tang H, Sharma M, Rajski J, Schuermyer C, Benware B (2006) A rapid yield learning flow based on production integrated layout-aware diagnosis. In: ITC. Paper 7.1

- Goldstein LH (1979) Controllability/observability analysis of digital circuits. IEEE Trans Circuits Syst CAS-26(9): 685–693

- Martin G, Scheffr L, Lavagno L (2005) Electronic Design Automation for Integrated Circuits Handbook. CRC Press, West Palm Beach, FL, USA, ISBN: 0849330963

- 11. Eichelberger EB, Williams TW (1977) A logic design structure for LSI testability. In: Proceedings of the Design Automatic Conference, June 1977, pp 462–468

- 12. Rajski J, Tyszer J, Kassab M, Mukherjee N (2004) Embedded deterministic test. IEEE Trans Comput Aided Design 23(5): 776–792

- 13. Touba NA (2006) Survey of test vector compression techniques. IEEE Design Test Comput 23(4): 294–303

- 14. Boppana V, Fuchs WK (1996) Partial scan design based on state transition modeling. In: Proceedings of the International Test Conference (ITC'96), p 538

- 15. IEEE Standard 1149.1–2001 (2001) Standard test access port and boundary-scan architecture. IEEE Standards Board

- 16. Oshana R (2002) Introduction to JTAG. In: EE Times Design, 29 October 2002

- Lu J-M, Wu C-W (2000) Cost and benefit models for logic and memory BIST. In: Proceedings of the DATE 2000, pp 710–714

- 18. Swanson B, Lange M (2004) At-speed testing made easy. In: EE Times, vol 3, June 2004

- Savir J, Patil S (1994) On broad-side delay test. In: Proceedings of the IEEE 12th VLSI Test Symposium (VTS 94), pp 284–290

- Bell G (2004) Growing challenges in nanometer timing analysis. In: EE Times, 18 October 2004

- Maliniak D (2005) Power integrity comes home to roost at 90 nm. In: EE Times, 03 February 2005

- 22. Williams TW, Brown NC (1981) Defect level as a function of fault coverage. IEEE Trans Comput C-30(12): 987–988

- Ma J, Lee J, Tehranipoor M (2009) Layout-aware pattern generation for maximizing supply noise effects on critical paths. In: Proceedings of IEEE 27th VLSI Test Symposium (VTS'09), pp 221–226

- 24. Ma J, Ahmed N, Tehranipoor M (2011) Low-cost diagnostic pattern generation and evaluation procedures for noise-related failures. In Proceedings of IEEE 29th VLSI Test Symposium (VTS'11), pp 309–314

- Ma J, Lee J, Ahmed N, Girard P, Tehranipoor M (2010) Pattern grading for testing critical paths considering power supply noise and crosstalk using a layout-aware quality metric. In: Proceedings of GLSVLSI'10, pp 127–130

- 26. Goel SK, Devta-Prasanna N, Ward M (2009) Comparing the effectiveness of deterministic bridge fault and multiple-detect stuck fault patterns for physical bridge defects: a simulation and silicon study. In: Proceedings of International Test Conference (ITC'09), pp 1–10

# Chapter 2

# **Hardware Implementation of Hash Functions**

Zhijie Shi, Chujiao Ma, Jordan Cote, and Bing Wang

# 2.1 Introduction to Cryptographic Hash Functions

Hash algorithm is a type of cryptographic primitives. Hash algorithms take as input a message of arbitrary length, and produce a *hash* or *message digest* as output. This process can be denoted as:

$$h = H(M)$$

.

where M is the input message and h is the hash generated by the hash algorithm H. Normally, the size of the hash h is fixed by the algorithm. For a cryptographic hash function, the hash length should be large enough to prevent an attack from finding two or more messages that generate the same hash. Currently, the most commonly used hash algorithms are MD5 [1] and SHA-2 [2].

In general, the cryptographic hash algorithms should have the following properties:

- 1. Preimage resistance. Given a hash h, it should be difficult to find a message M such that h = H(M). This is part of the one-way property. It is easy to compute the hash from a message, but it is extremely difficult to deduce a message from the hash.

- 2. Second preimage (or 2nd-preimage) resistance. Given a message  $M_1$ , it is difficult to find another message  $M_2$  such that  $M_1$  and  $M_2$  generate the same hash. Any change in the input results in changes, often wild changes, in the hash.

- 3. Collision resistance. It should be difficult to find two messages  $M_1$  and  $M_2$  such that  $M_1 \neq M_2$ , but  $H(M_1) = H(M_2)$ .

A hash function that is both preimage resistant and 2nd-preimage resistant is called a one-way hash function. Note that preimage resistance does not imply 2nd-preimage

Computer Science and Engineering Department, University of Connecticut, Storrs, CT, USA e-mail: zshi@engr.uconn.edu; chujiao.ma@engr.uconn.edu; cote@engr.uconn.edu; bing@engr.uconn.edu

Z. Shi  $(\boxtimes) \cdot C$ . Ma  $\cdot$  J. Cote  $\cdot$  B. Wang

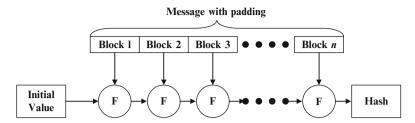

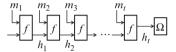

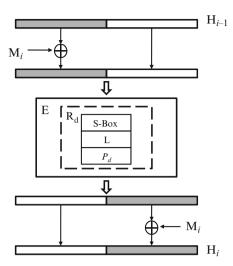

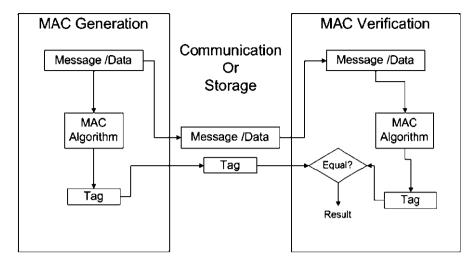

Fig. 2.1 The Merkle-Damgård model of hash functions

resistance, and vice versa. If a hash function is collision resistant (and thus also 2nd-preimage resistant), it is a collision resistant hash function (CRHF). Although collision resistance does not guarantee preimage resistance, most CRHFs in practice appear to be preimage resistant [3].

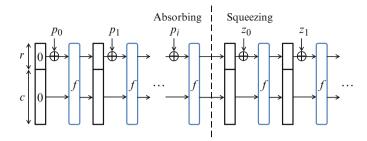

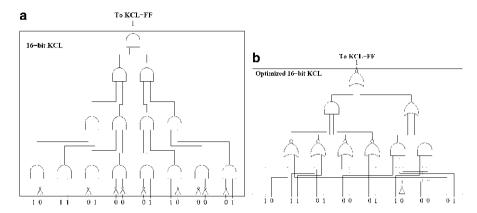

## 2.1.1 Construction of Hash Functions

Hash function can be constructed in several ways. The Merkle-Damgård model, illustrated in Fig. 2.1, has shown good properties over the years [4], and has been adopted in the design of many successful hash functions such as MD5 and SHA-2. In this model, the message is padded and divided into blocks of uniform length. The blocks are then processed sequentially with a compression function F. Starting with an initial hash, F repeatedly generates a new intermediate hash value from the previous one and a new message block. The output of the final compression function is the hash of the message. The Merkle-Damgård model makes it easy to manage large inputs and produce a fixed-length output. The security of this scheme relies on the security of the compression function F. It can be proven that if the compression F is collision resistant then the hash function constructed from the Merkle-Damgård model is also collision resistant [4].

MD5, SHA-2, and their variants are the most popular hash algorithms. They follow the Merkle-Damgård model and use logic operations such as AND, OR, and XOR in their compression functions. Recently, collision pairs have been found for MD5, SHA-0 and SHA-1 [5–8], making these algorithms vulnerable to attacks because they do not have the collision resistance property. Although no successful attacks have been reported for algorithms in the SHA-2 family, e.g., SHA-256 and SHA-512, these algorithms may be vulnerable to the same type of attacks because they are designed with similar principles: a Merkle-Damgård model with a compression function consisting of logic operations. Thus, it is imperative to study new compression functions and even new construction models for fast and secure hash functions. In fact, National Institute of Standards and Technology (NIST) held a public competition to select new hash algorithm, SHA-3, starting from 2007 [9].

SHA-3 is expected to be more secure than SHA-2. New hash design techniques are also adopted in many SHA-3 candidates. We will look at some of the candidates later in this chapter.

A hash function can also be constructed from a symmetric-key cipher, such as DES or AES. Several schemes have been proposed to turn a block cipher into a hash function. These scheme include Davies-Meyer, Matyas-Meyer-Oseas [10], and Miyaguchi-Preneel schemes [5,6,11,12]. The Miyaguchi-Preneel scheme also has an iterative structure. It starts with an initial hash and updates the hash when a block of message is processed. The scheme can be expressed as  $h' = E_{g(h)}(M_i) \oplus h \oplus M_i$ , where  $M_i$  is message block i, h the hash before  $M_i$  is processed, h' the updated hash after  $M_i$  is processed, and g() is a function that converts h to a key for the block cipher E.

Another notable algorithm is Whirlpool, a hash function constructed with the Miyaguchi-Preneel scheme [13]. It has been recommended by the New European Schemes for Signatures, Integrity, and Encryption (NESSIE) project and adopted by International Organization for Standardization (ISO) as part of ISO 10118–3. The block cipher in Whirlpool is a dedicated cipher called W, which is similar to the AES algorithm despite significant differences. No successful attacks to Whirlpool have been found so far. However, the Whirlpool algorithm is much slower than other hash algorithms. For example, on Pentium III, Whirlpool's performance is 36.5 cycles/byte while MD5's is 3.7 cycles/byte and SHA-1's is 8.3 cycles/byte [14].

## 2.1.2 Application of Hash Functions

Hash algorithms can be used to verify data integrity. After receiving data, one can compute the hash of the received data, and compare it with the hash of the original data, which may be sent through secure channels or obtained from a trusted source. If they are the same, there is a high confidence level that the message was not modified during the transmission (because of the 2nd-preimage resistance). Nowadays, many software download sites provide the MD5 or SHA-2 hash of the software available for downloading.

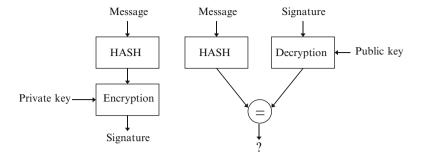

Hash algorithms can also be used together with public-key algorithms to generate digital signatures. For example, Alice can sign a document by encrypting the hash of the message with her private key. The ciphertext can be used as Alice's signature. Anyone who wants to verify the signature can decrypt the ciphertext with Alice's public key, and compare the decrypted value with the hash generated from the message. This process is shown in Fig. 2.2. The left part of the figure generates the signature with Alice's private key, and the right part checks the signature with her public key.

Hash algorithms can be used for authentication as well. In this case, the hash value of the user's password, instead of the password itself, is transmitted and compared by the server. When computing the hash, the password may be concatenated with a random value generated by the server. Hence, the hashes are different every time, preventing an attacker sniffing on the network traffic

Fig. 2.2 Application of hash algorithm in digital signature

from reusing an old hash. For example, the Challenge-Handshake Authentication Protocol (CHAP) [15] uses this approach in the Point-to-Point Protocol (PPP) [16] for dial-up Internet connections.

Hash algorithms can also be used in Hash-based Message Authentication Code algorithms [17] have been used in many systems to provide both data integrity and message authentication, especially in resource constrained environments where public-key algorithms are too slow and energy consuming.

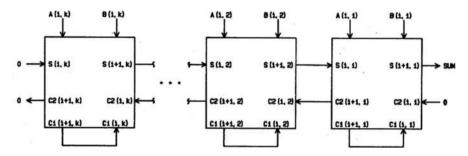

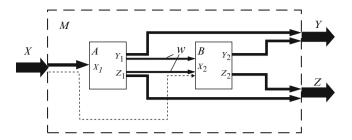

#### 2.2 Hardware Implementation of Hash Functions

MD5 and SHA-2 (more specifically SHA-256) are commonly used hash functions today. Both of them adopt the Merkle-Damgård construction. As they have much in common, many optimization techniques can be applied to both algorithms.

#### 2.2.1 MD5

MD5 is a common Merkle-Damgård-based hash function. A MD5 block has 512 bits, which can be divided into sixteen 32-bit words  $(M_0, \ldots, M_{15})$ . The internal hash state has 128 bits, which are stored as four 32-bit words and denoted by the 4-tuple (A, B, C, D), and is initially set to a predetermined initialization vector. The basic computation unit of MD5 is called a step. Each step alters the state variables (A, B, C, D), as shown in Equation 2.1, using a compression function F that takes B, C, and D as input and generates a 32-bit value as output. In the equation,  $\ll$  indicates the left rotation operation and  $W \ll S$  rotates bits in W to left by S. In total, MD5 has 64 steps. The first 16 steps are called round one, the next 16 round two, and so on. Rounds also have distinct compression functions, as specified in Equation 2.2, where i is the step number.

**Table 2.1** A 3-stage MD5 pipeline

| Steps        | Computation of B                                     |

|--------------|------------------------------------------------------|

| Step i       | $B_i = B_{i-1} + (AKM_i + F(B_{i-1}, C, D)) \ll S_i$ |

| Step $i + 1$ | $AKM_{i+1} = M_i + 1 + (AK_{i+1})$                   |

| Step $i + 2$ | $AK_{i+2} = (K_{i+2} + B_{i-1})$                     |

$$A_{\text{new}} = D$$

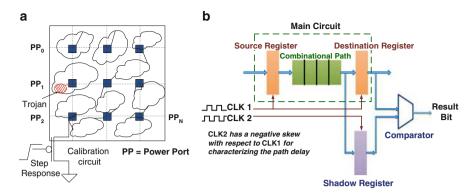

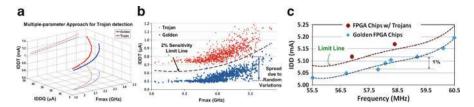

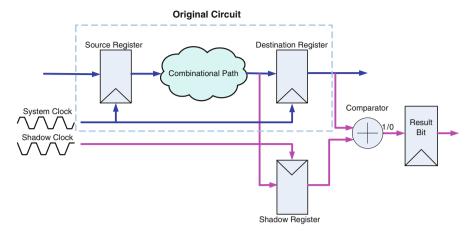

$$B_{\text{new}} = B + (M_i + K_i + A + F(B, C, D)) \ll S_i$$

$$C_{\text{new}} = B$$

$$D_{\text{new}} = C$$

$$(2.1)$$

$$F(B,C,D) = \begin{cases} (B \land C) \lor (\neg B \land D) & : 0 \le i \le 15\\ (B \land C) \lor (C \land \neg D) & : 16 \le i \le 31\\ B \oplus C \oplus D & : 32 \le i \le 47\\ C \oplus (B \land \neg D) & : 48 \le i \le 63 \end{cases}$$

(2.2)

$$M_{i} = \begin{cases} M_{i} & : 0 \le i \le 15 \\ M_{5i+1 \pmod{16}} & : 16 \le i \le 31 \\ M_{3i+5 \pmod{16}} & : 32 \le i \le 47 \\ M_{7i \pmod{16}} & : 48 \le i \le 63 \end{cases}$$

$$(2.3)$$

As there are only 16 words in a message block, each word is used four times in the 64 steps. The message scheduler, Equation 2.3, determines which of the 16 message words  $M_i$  is used in a particular step i. For example, round one simply uses word  $M_i$  for step i, while round two uses  $M_{5i+1(mod16)}$ . Furthermore,  $K_0, \ldots, K_{63}$  and  $S_0, \ldots, S_{63}$  are predetermined constant values. After the completion of all 64 steps, the latest values (A, B, C, D) are added to the input values (A, B, C, D) of the block, using modulo  $2^{32}$  addition. That sum is the updated hash value and serves as the input hash value for the next message block (512 bits) if there is one. The final hash is the concatenation of A, B, C, and D generated from the last block. The specification for MD5 was presented in [1].

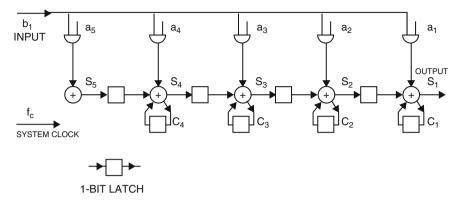

#### 2.2.1.1 Pipelining

The operations in each step of MD5 are not complicated. When implemented in hardware, the number of operations that can be done in parallel is limited by data dependency. The data dependency between the state variables of MD5 allows for interesting pipelining applications. In particular, since only B is updated in a step and other words are not, one may use data forwarding as described in [18]. Because some future values of A are known, the computation of  $B_{i+1}$  and  $B_{i+2}$  may start early. As shown in Table 2.1, the updated values of B can be computed in three stages. When  $B_i$  is computed in step i,  $AKM_{i+1}$  in step i+1 and  $AK_{i+2}$  in step i+2 can be computed in parallel for  $B_{i+1}$  and  $B_{i+2}$ .

Another approach to MD5 pipelining is to take advantage of the independency among rounds. For example, in a 4-stage pipeline with one stage dedicated to each

| Type                                     | Block latency (ns) | Throughput (Mbps) |

|------------------------------------------|--------------------|-------------------|

| Iterative [21]                           | 843                | 607               |

| Pipelined (64 stage) [21]                | 706                | 725               |

| Parallel (10x) [21]                      | 875                | 5,857             |

| Pipelined (3 stage) [18]                 | _                  | 746               |

| Iterative [19]                           | 633                | 810               |

| Pipelined (32 stage) [19]                | 764                | 21,428            |

| Pipelined (32 stage), Loop unrolled [19] | 511                | 32,035            |

Table 2.2 FPGA implementations of MD5

round, the 16 steps in each round are computed iteratively within a stage. Therefore, the stages are much longer. One extension to this architecture is to unroll the loop for the 16 steps in each stage, requiring dedicated logic for each step rather than reusing logic for 16 steps in a pipeline stage. There are also performance gains as the results of the reduction in clock and register delay [19].

#### 2.2.1.2 Other Optimizations

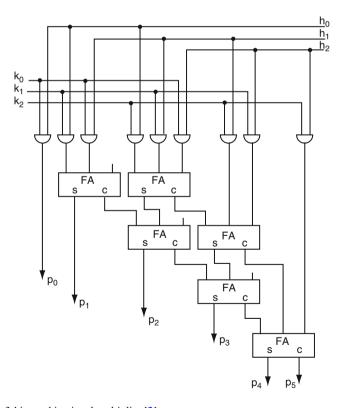

Carry save adders (CSA) are commonly used as an alternative to the full adder when there are multiple numbers to be added. A CSA is much smaller and faster than a regular adder because it does not require carry propagation. A regular adder is needed only at the end of a series of CSA additions. However, in FPGA implementations, the utility of using CSA is diminished since some platforms incorporate partial addition optimizations which allow ripple carry adders to perform just as well while using less area [20].

If the hash function is being implemented in FPGA, block RAM can be used to improve performance. Block RAM is a dedicated part of the chip which may be used to store constants. This takes the burden off the combinatorial logic blocks, freeing them for other purposes. This means that more CLBs are available to the routing algorithm, resulting in more direct routes and faster performance.

#### 2.2.1.3 MD5 Performance

Table 2.2 lists some fast MD5 implementations. The FPGA implementations have reached extremely high throughput up to 32 Gbps. The reader should exercise caution while reviewing these numbers, as a high throughput does not imply a low latency. This is especially true for parallel block implementations. Processing blocks for a single message cannot be done in parallel since they are dependent on each other. Instead, a parallel block implementation is similar to using multiple processing units with independent input streams. Hence, the configuration is only useful when the input is parallel in nature.

| Table 2.3 SHA-2 state varia                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | ables, compression functions, and message scheduler                  |  |  |  |

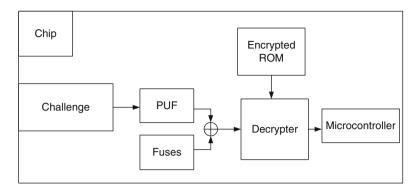

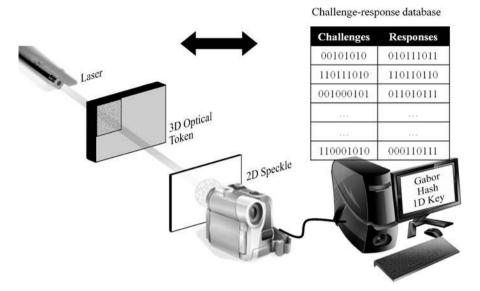

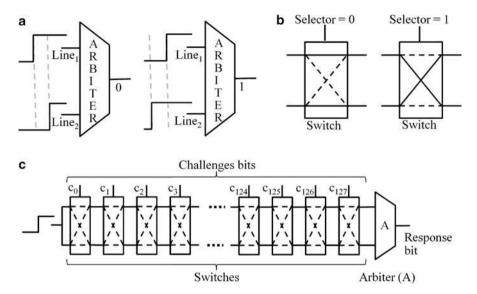

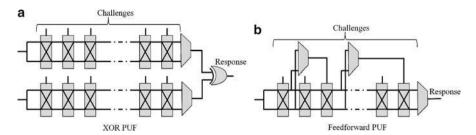

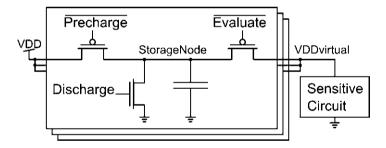

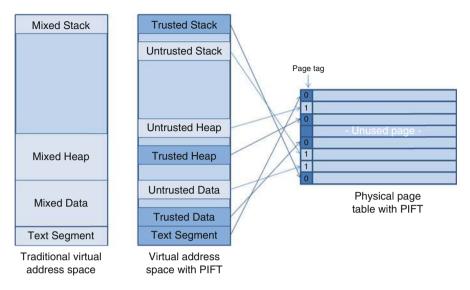

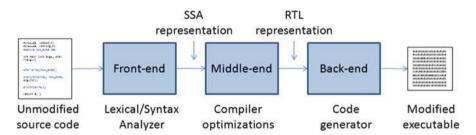

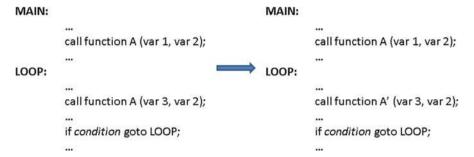

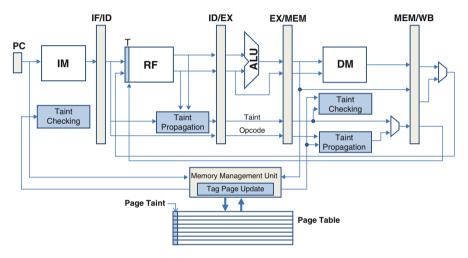

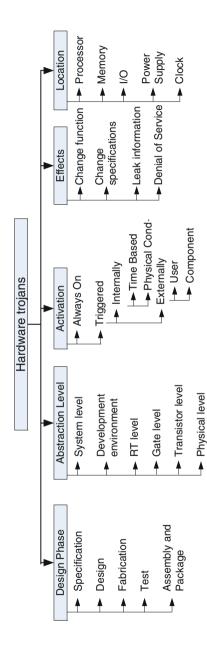

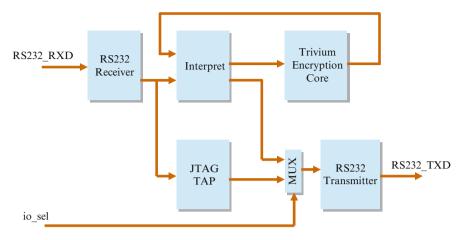

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------|--|--|--|