INTRODUCTION TO

# 80x86 Assembly Language and Computer Architecture

# RICHARD C. DETMER

JONES AND BARTLETT COMPUTER SCIENCE

INTRODUCTION TO

# 80x86 Assembly Language and Computer Architecture

# **RICHARD C. DETMER** Middle Tennessee State University

JONES AND BARTLETT PUBLISHERS Sudbury, Massachusetts BOSTON TORONTO LONDON SINGAPORE

World Headquarters Jones and Bartlett Publishers 40 Tall Pine Drive Sudbury, MA 01776 978-443-5000 info@jbpub.com www.jbpub.com

Jones and Bartlett Publishers Canada 2406 Nikanna Road Mississauga, ON L5C 2W6 CANADA Jones and Bartlett Publishers International Barb House, Barb Mews London W6 7PA UK

Copyright © 2001 by Jones and Bartlett Publishers, Inc.

Cover Image © Stone/Peter Poulides

#### Library of Congress Cataloging-in-Publication Data

Detmer, Richard C.

Introduction to 80x86 Assembly Language and Computer Architecture / Richard Detmer.

p. cm.

Includes index.

ISBN 0-7637-1773-8

1. Computer architecture. 2. Assembler language (Computer program language) I.

Title.

QA76.9.A73 D48 2001 004.2'2—dc21

00-069028

All rights reserved. No part of the material protected by this copyright notice may be reproduced or utilized in any form, electronic or mechanical, including photocopying, recording, or any information storage or retrieval system, without written permission from the copyright owner.

Senior Acquisitions Editor: Michael Stranz Development and Product Manager: Amy Rose Production Assistant: Tara McCormick Production Coordination: Trillium Project Management Composition: Northeast Compositors, Inc. Copyeditor: Sarah Corey Text Design: Dartmouth Publishing, Inc. Cover Design: Kristin Ohlin Printing and Binding: Courier Westford Cover printing: John Pow Company

This book was typeset in Quark 4.1 on a Macintosh G4. The font families used were Serifa, Frutiger, and Courier. The first printing was printed on 50# Decision 94 Opaque.

Printed in the United States of America 05 04 03 02 01 10 9 8 7 6 5 4 3 2 1

Dedicated to

my mother, Emma Langenhop Detmer Baldwin Toombs and my uncle, Carl E. Langenhop both of whom encouraged me to become a scholar.

# PREFACE

A computer can be viewed from many different levels. Many people are interested only in using applications such as word processing or games. A computer programmer, however, often sees the computer as an instrument to create new applications software. A high-level language programmer's image of the computer is provided by the language compiler, which gives the impression that the computer stores object types like integer, real, and array of char in named memory locations, calculates values of expressions, calls procedures, executes while loops, and so forth.

However, an actual computer works at even lower levels. This book emphasizes the architectural level, that is, the level defined by the machine instructions that the processor can execute. Assembly-language instructions translate directly into machinelanguage instructions, so that when you write an assembly-language program, you gain an understanding of how the computer works at the machine-language level.

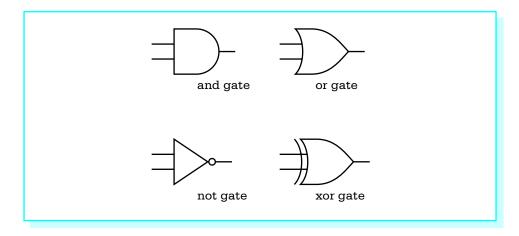

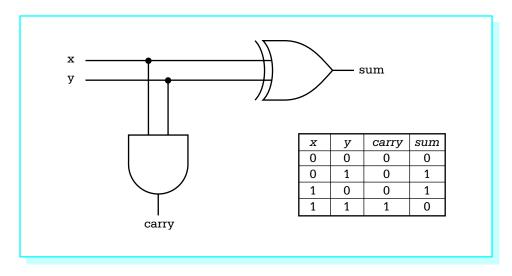

Although this book emphasizes the assembly-language/machine-language level of computer operations, it also looks at other levels. For instance, it describes how highlevel language concepts such as if statements are realized at the machine level. It discusses some of the functions of the operating system. It briefly describes the logic gates that are used at the hardware level. It also looks at how assembly language is translated into machine language.

To program effectively at any level, programmers must understand certain fundamental principles at the machine level. These apply to most computer architectures. *Introduction to 80x86 Assembly Language and Computer Architecture* teaches these fundamental concepts:

- memory addressing, CPU registers and their uses

- representation of data in a computer in numeric formats and as character strings

- instructions to operate on 2's complement integers

- instructions to operate on individual bits

- instructions to handle strings of characters

- instructions for branching and looping

- coding of procedures: transfer of control, parameter passing, local variables, and preserving the environment for the calling program

The primary architecture covered is the Intel 80x86 CPU family used in many personal computers. However, almost every chapter includes information about other architectures, or about different computer levels. Programming in assembly language and studying related concepts in *Introduction to 80x86 Assembly Language and Computer Architecture* prepares the student to program effectively in any programming language, to pursue advanced studies in computer design and architecture, or to learn more about system details for specific computers.

#### **Text Organization and Content**

Much of the material in this book is based on my previous book, *Fundamentals of* Assembly Language Programming Using the IBM PC and Compatibles. While teaching this material through the years, I have increasingly come to the conclusion that an assembly language course is the best place to introduce computer architecture to most students. This book reflects a stronger emphasis on architecture than on programming. It also concentrates on general concepts as opposed to the details of a particular computer system.

The minimal prerequisite for my assembly language class is a good understanding of a structured high-level language. Chapters 3 through 6 and Chapter 8 form the core of my one-semester course. I normally cover Chapters 1–8 thoroughly, Chapter 9 quickly, and then choose topics from Chapters 10–12 depending on time and resources available. For instance, I sometimes introduce floating-point operations via in-line assembly statements in a C++ program.

#### **Style and Pedagogy**

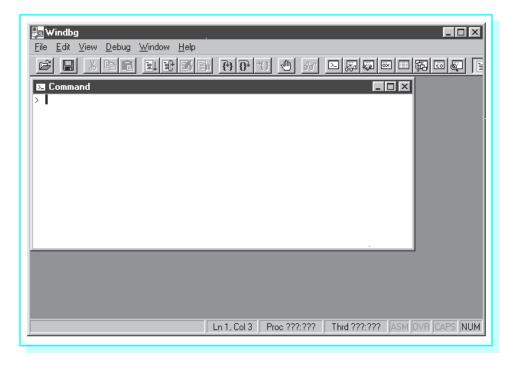

The text primarily teaches by example. A complete assembly-language program is presented very early, in Chapter 3, and its components are carefully examined at a level that the student is able to understand. Subsequent chapters include many examples of assembly language code along with appropriate explanations of new or difficult concepts.

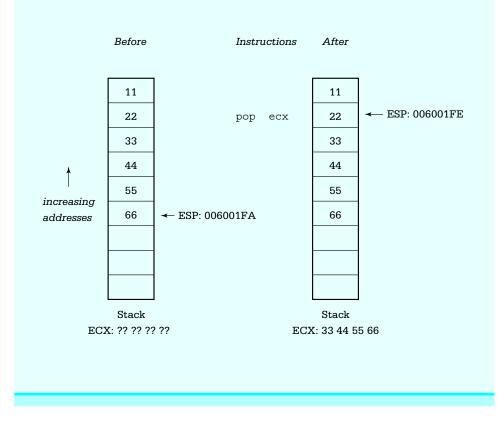

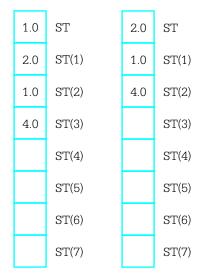

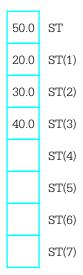

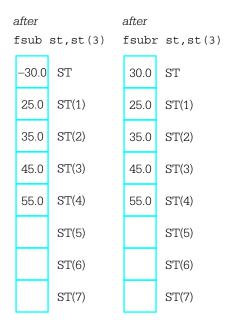

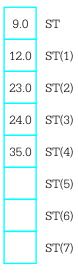

The text uses numerous figures and examples. Many series of "before" and "after" examples are given for instructions. Examples are included that illustrate the use of a debugger. These examples give the student a stronger sense of what is happening inside the computer.

Exercises appear at the end of each section. Short-answer exercises reinforce understanding of the material just covered, and programming exercises offer an opportunity to apply the material to assembly-language programs.

#### **Software Environment**

The "standard" 80x86 assembler is Microsoft's Macro Assembler (MASM), version 6.11. Although this assembler can produce code for 32-bit flat memory model programming appropriate to a Windows 95, Windows NT, or other 32-bit Microsoft operating system environment, the linker and debugger that come with this software package are not suitable for use in such an environment. This book comes with a CD containing the assembler program from MASM (ML), a more recent Microsoft linker, the 32-bit full-screen debugger WinDbg (also from Microsoft), and necessary supporting files. This software package provides a good environment for producing and debugging console applications.

The CD included with the book also contains a package designed to simplify input/output for the student, so that the emphasis remains on architecture rather than operating system details. This I/O package is used extensively through most of the book. Finally, the CD contains source code for each program that appears as a figure in the book.

#### **Instructor's Support**

Supplementary materials for this book include an Instructor's Guide that contains some teaching tips and solutions to many exercises. In addition, the author can be contacted at rdetmer@mtsu.edu with questions or comments.

#### Acknowledgments

I would like to thank my students who suffered through preliminary versions of this text, often getting materials that were duplicated "just in time." These students were very good at catching errors. I also want to thank Hong Shi Yuan, who used a preliminary version of this text in his assembly language class and who offered valuable feedback.

Many thanks to the following people who took the time to review the manuscript: Dennis Bouvier, University of Houston–Clear Lake; Barry Fagin, US Air Force Academy; Glynis Hamel, Worcester Polytechnic Institute; Dennis Fairclough, Utah Valley State College; Thomas Higginbotham, Southeastern Louisiana University; Clifford Nadler, Worcester Polytechnic Institute.

My wife, Carol, deserves credit for her understanding during the many hours that I ignored her and word-processed at my computer.

Richard C. Detmer

# CONTENTS

Preface v

#### Chapter 1 Representing Data in a Computer 1

- 1.1 Binary and Hexadecimal Numbers 2

- 1.2 Character Codes 6

- 1.3 2's Complement Representation for Signed Integers 9

- 1.4 Addition and Subtraction of 2's Complement Numbers 15

- 1.5 Other Systems for Representing Numbers 21

Chapter Summary 25

#### Chapter 2 Parts of a Computer System 27

- 2.1 PC Hardware: Memory 28

- 2.2 PC Hardware: The CPU 30

- 2.3 PC Hardware: Input/Output Devices 36

- 2.4 PC Software 37

PC Software: The Operating System 37

- PC Software: Text Editors 38

- PC Software: Language Translators and the Linker 38

Chapter Summary 39

#### Chapter 3 Elements of Assembly Language 41

- 3.1 Assembly Language Statements 42

- 3.2 A Complete Example 45

- 3.3 How to Assemble, Link, and Run a Program 53

- 3.4 The Assembler Listing File 60

- 3.5 Constant Operands 68

- 3.6 Instruction Operands 73

3.7 Input/Output Using Macros Defined in IO.H 77Chapter Summary 82

#### Chapter 4 Basic Instructions 85

- 4.1 Copying Data 86

- 4.2 Integer Addition and Subtraction Instructions 95

- 4.3 Multiplication Instructions 108

- 4.4 Division Instructions 118

- 4.5 Addition and Subtraction of Larger Numbers 130

- 4.6 Something Extra: Levels of Abstraction and Microcode 133Chapter Summary 134

- Chapter Summary

#### Chapter 5 Branching and Looping 137

- 5.1 Unconditional Jumps 138

- 5.2 Conditional Jumps, Compare Instructions, and if Structures 144

- 5.3 Implementing Loop Structures 159

- 5.4 for Loops in Assembly Language 173

- 5.5 Arrays 180

- 5.6 Something Extra: Pipelining 189 Chapter Summary 190

#### Chapter 6 Procedures 193

- 6.1 The 80x86 Stack 194

- 6.2 Procedure Body, Call and Return 201

- 6.3 Parameters and Local Variables 211

- 6.4 Recursion 223

- 6.5 Other Architectures: Procedures Without a Stack 228 Chapter Summary 230

#### Chapter 7 String Operations 231

- 7.1 Using String Instructions 232

- 7.2 Repeat Prefixes and More String Instructions 239

- 7.3 Character Translation 254

- 7.4 Converting a 2's Complement Integer to an ASCII String 259

- 7.5 Other Architectures: CISC versus RISC Designs 264 Chapter Summary 265

#### Chapter 8 Bit Manipulation 267

- 8.1 Logical Operations 268

- 8.2 Shift and Rotate Instructions 278

- 8.3 Converting an ASCII String to a 2's Complement Integer 292

- 8.4 The Hardware Level—Logic Gates 298 Chapter Summary 299

#### Chapter 9 The Assembly Process 301

- 9.1 Two-Pass and One-Pass Assembly 302

- 9.2 80x86 Instruction Coding 307

- 9.3 Macro Definition and Expansion 319

- 9.4 Conditional Assembly 326

- 9.5 Macros in IO.H 333

- Chapter Summary 337

#### Chapter 10 Floating-Point Arithmetic 339

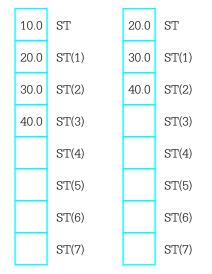

- 10.1 80x86 Floating-Point Architecture 340

- 10.2 Programming with Floating-Point Instructions 359

- 10.3 Floating-Point Emulation 374

- 10.4 Floating-Point and In-line Assembly 384

- Chapter Summary 386

#### Chapter 11 Decimal Arithmetic 387

- 11.1 Packed BCD Representations 388

- 11.2 Packed BCD Instructions 396

- 11.3 Unpacked BCD Representations and Instructions 404

- 11.4 Other Architectures: VAX Packed Decimal Instructions 416

- Chapter Summary 417

#### Chapter 12 Input/Output 419

- 12.1 Console I/O Using the Kernel32 Library 420

- 12.2 Sequential File I/O Using the Kernel32 Library 428

- 12.3 Lower-Level Input/Output 437

- Chapter Summary 439

| Appendix A | Hexadecimal/ASCII Conversion 441     |  |  |  |  |  |

|------------|--------------------------------------|--|--|--|--|--|

| Appendix B | Useful MS-DOS Commands 443           |  |  |  |  |  |

| Appendix C | MASM 6.11 Reserved Words 445         |  |  |  |  |  |

| Appendix D | 80x86 Instructions (by Mnemonic) 449 |  |  |  |  |  |

| Appendix E | 80x86 Instructions (by Opcode) 469   |  |  |  |  |  |

| Index 489  |                                      |  |  |  |  |  |

# CHAPTER

Representing Data in a Computer

When programming in a high-level language like Java or C++, you use variables of different types (such as integer, float, or character). Once you have declared variables, you don't have to worry about how the data are represented in the computer. When you deal with a computer at the machine level, however, you must be more concerned with how data are stored. Often you have the job of converting data from one representation to another. This chapter covers some common ways that data are represented in a microcomputer. Chapter 2 gives an overview of microcomputer hardware and software. Chapter 3 illustrates how to write an assembly language program that directly controls execution of the computer's native instructions.

- **1.1** Binary and hexadecimal numbers

- **1.2** Character codes

- **1.3** 2's complement representation for signed integers

- **1.4** Addition and subtraction of 2's complement numbers

- **1.5** Other systems for representing numbers

#### **1.1** Binary and Hexadecimal Numbers

A computer uses **bits** (binary digits, each an electronic state representing zero or one) to denote values. We represent such **binary** numbers using the digits 0 and 1 and a base 2 place-value system. This binary number system is like the decimal system except that the positions (right to left) are 1's, 2's, 4's, 8's, 16's (and higher powers of 2) instead of 1's, 10's, 100's, 1000's, 10000's (powers of 10). For example, the binary number 1101 can be interpreted as the decimal number 13,

| 1     |   | 1     |   | 0    |   | 1     |   |    |

|-------|---|-------|---|------|---|-------|---|----|

| one 8 | + | one 4 | + | no 2 | + | one 1 | = | 13 |

Binary numbers are so long that they are awkward to read and write. For instance, it takes the eight bits 11111010 to represent the decimal number 250, or the fifteen bits 111010100110000 to represent the decimal number 30000. The **hexadecimal** (base 16) number system represents numbers using about one-fourth as many digits as the binary system. Conversions between hexadecimal and binary are so easy that **hex** can be thought of as shorthand for binary. The hexadecimal system requires sixteen digits. The digits 0, 1, 2, 3, 4, 5, 6, 7, 8, and 9 are used just as in the decimal system; A, B, C, D, E, and F are used for the decimal numbers 10, 11, 12, 13, 14, and 15, respectively. Either uppercase or lowercase letters can be used for the new digits.

The positions in hexadecimal numbers correspond to powers of 16. From right to left, they are 1's, 16's, 256's, etc. The value of the hex number 9D7A is 40314 in decimal since

| 9    | π | 4096 | 36864   | $[4096 = 16^3]$                  |

|------|---|------|---------|----------------------------------|

| + 13 | π | 256  | 3328    | $[D \text{ is } 13, 256 = 16^2]$ |

| + 7  | π | 16   | 112     |                                  |

| + 10 | π | 1    | 10      | [ A is 10 ]                      |

|      |   |      | = 40314 |                                  |

Figure 1.1 shows small numbers expressed in decimal, hexadecimal, and binary systems. It is worthwhile to memorize this table or to be able to construct it very quickly.

You have seen above how to convert binary or hexadecimal numbers to decimal. How can you convert numbers from decimal to hex? From decimal to binary? From binary to hex? From hex to binary? We'll show how to do these conversions manually, but often the easiest way is to use a calculator that allows numbers to be entered in deci-

| Decimal | Hexadecimal | Binary |

|---------|-------------|--------|

| 0       | 0           | 0      |

| 1       | 1           | 1      |

| 2       | 2           | 10     |

| 3       | 3           | 11     |

| 4       | 4           | 100    |

| 5       | 5           | 101    |

| 6       | 6           | 110    |

| 7       | 7           | 111    |

| 8       | 8           | 1000   |

| 9       | 9           | 1001   |

| 10      | A           | 1010   |

| 11      | В           | 1011   |

| 12      | С           | 1100   |

| 13      | D           | 1101   |

| 14      | E           | 1110   |

| 15      | F           | 1111   |

#### Figure 1.1 Decimal, hexadecimal, and binary numbers

mal, hexadecimal, or binary. Conversion between bases is normally a matter of pressing a key or two. These calculators can do arithmetic directly in binary or hex as well as decimal and often have a full range of other functions available. One warning: Many of these calculators use seven segment displays and display the lowercase letter b so that it looks almost like the numeral 6. Other characters may also be difficult to read.

A calculator isn't needed to convert a hexadecimal number to its equivalent binary form. In fact, many binary numbers are too long to be displayed on a typical calculator. Instead, simply substitute four bits for each hex digit. The bits are those found in the third column of Fig. 1.1, padded with leading zeros as needed. For example,

3B8E2<sub>16</sub> = 11 1011 1000 1110 0010<sub>2</sub>

The subscripts 16 and 2 are used to indicate the base of the system in which a number is written; they are usually omitted when there is little chance of confusion. The extra spaces in the binary number are just to make it more readable. Note that the rightmost

hex digit 2 was converted to 0010, including leading zeros. While it's not necessary to convert the leading 3 to 0011, the conversion would have been correct since leading zeros do not change the value of a binary number.

To convert binary numbers to hexadecimal format, reverse the above steps: Break the binary number into groups of four bits, starting from the right, and substitute the corresponding hex digit for each group of four bits. For example,

1011011101001101111 = 101 1011 1010 0110 1111 = 5BA6F

You have seen how to convert a binary number to an equivalent decimal number. However, instead of converting a long binary number directly to decimal, it is faster to convert it to hex, and then convert the hex number to decimal. Again, using the above 19-bit-long number,

> $1011011101001101111_{2}$ = 101 1011 1010 0110 1111 = 5BA6F\_{16} = 5 \pi 65536 + 11 \pi 4096 + 10 \pi 256 + 6 \pi 16 + 15 \pi 1 = 375407\_{10}

The following is an algorithm for converting a decimal number to its hex equivalent. It produces the hex digits of the answer right to left. The algorithm is expressed in pseudocode, which is the way that algorithms and program designs will be written in this book.

```

until DecimalNumber = 0 loop

divide DecimalNumber by 16, getting Quotient and Remainder;

Remainder (in hex) is the next digit (right to left);

DecimalNumber := Quotient;

```

end until;

#### Example

As an example, the decimal-to-hex algorithm is traced for the decimal number 5876:

• Since this is an until loop, the controlling condition is not checked until after the body has been executed the first time.

Divide 16 into 5876 (DecimalNumber). the new value for DecimalNumber 367 Quotient 16)5876 5872 4 Remainder the rightmost digit of the answer Result so far: 4 367 is not zero. Divide it by 16. 22 Quotient the new value for DecimalNumber 16)367 352 15 Remainder the second digit of the answer Result so far: F4 • 22 is not zero. Divide it by 16. 1 Quotient the new value for DecimalNumber 16)22 16 6 Remainder the next digit of the answer Result so far: 6F4 1 is not zero. Divide it by 16. the new value for DecimalNumber 0 Ouotient 16)1 $\frac{0}{1}$ Remainder the next digit of the answer Result so far: 16F4 • 0 is zero, so the until loop terminates. The answer is 16F4<sub>16</sub>

The **octal** (base 8) number system is used with some computer systems. Octal numbers are written using digits 0 through 7. Most calculators that do hex arithmetic also handle octal values. It is easy to convert a binary number to octal by writing the octal equivalent for each group of three bits, or to convert from octal to binary by replacing each octal digit by three bits. To convert from decimal to octal, one can use an algorithm that is the same as the decimal to hex scheme except that you divide by 8 instead of 16 at each step.

#### **Exercises 1.1**

Complete the table below by supplying the missing two forms for each number.

|     | Binary      | Hexadecimal | Decimal |

|-----|-------------|-------------|---------|

| 1.  | 100         |             |         |

| 2.  | 10101101    |             |         |

| 3.  | 1101110101  |             |         |

| 4.  | 11111011110 |             |         |

| 5.  | 1000000001  |             |         |

| 6.  |             | 8EF         |         |

| 7.  |             | 10          |         |

| 8.  |             | A52E        |         |

| 9.  |             | 70C         |         |

| 10. |             | 6BD3        |         |

| 11. |             |             | 100     |

| 12. |             |             | 527     |

| 13. |             |             | 4128    |

| 14. |             |             | 11947   |

| 15. |             |             | 59020   |

|     |             |             |         |

#### **1.2** Character Codes

Letters, numerals, punctuation marks, and other characters are represented in a computer by assigning a numeric value to each character. Several schemes for assigning these numeric values have been used. The system commonly used with microcomputers is the American Standard Code for Information Interchange (abbreviated **ASCII** and pronounced ASK-ee).

The ASCII system uses seven bits to represent characters, so that values from 000 0000 to 111 1111 are assigned to characters. This means that 128 different characters can be represented using ASCII codes. The ASCII codes are usually given as hex numbers from 00 to 7F or as decimal numbers from 0 to 127.<sup>1</sup> Appendix A has a complete listing of ASCII codes. Using this table, you can check that the message

Computers are fun.

**<sup>1</sup>** Some computers, including the IBM PC and compatible systems, use an extended character set, additionally assigning characters to hex numbers 80 to FF (decimal 128 to 255). Extended character sets will not be used in this book.

can be coded in ASCII, using hex numbers, as

| 43 | 6F | 6D | 70 | 75 | 74 | 65 | 72 | 73 | 20 | 61 | 72 | 65 | 20 | 66 | 75 | 6E | 2E |

|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|

| С  | 0  | m  | р  | u  | t  | е  | r  | ន  |    | а  | r  | е  |    | f  | u  | n  |    |

Note that a space, even though it is invisible, has a character code (hex 20).

Numbers can be represented using character codes. For example, the ASCII codes for the date October 21, 1976 are

| 4F | 63 | 74 | 6F | 62 | 65 | 72 | 20 | 32 | 31 | 2C | 20 | 31 | 39 | 37 | 36 |

|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|

| 0  | С  | t  | 0  | b  | е  | r  |    | 2  | 1  | ,  |    | 1  | 9  | 7  | 6  |

with the number 21 represented using ASCII codes 32 31, and 1976 represented using 31 39 37 36. This is very different from the binary representation in the last section, where  $21_{10} = 10101_2$  and  $1970_{10} = 11110111000_2$ . Computers use both of these representations for numbers: ASCII for input and output, and binary for internal computations.

The ASCII code assignments may seem rather arbitrary, but there are certain patterns. The codes for uppercase letters are contiguous, as are the codes for lowercase letters. The codes for an uppercase letter and the corresponding lowercase letter differ by exactly one bit. Bit 5 is 0 for an uppercase letter and 1 for the corresponding lowercase letter while other bits are the same. (Bits in most computer architectures are numbered right to left, starting with 0 for the rightmost bit.) For example,

- uppercase M codes as 4D<sub>16</sub> = 1001101<sub>2</sub>

- lowercase m codes as 6D<sub>16</sub> = 1101101<sub>2</sub>

The **printable characters** are grouped together from  $20_{16}$  to  $7E_{16}$ . (A space is considered a printable character.) Numerals 0, 1, ..., 9 have ASCII codes  $30_{16}$ ,  $31_{16}$ , ...,  $39_{16}$ , respectively.

The characters from  $00_{16}$  to  $1F_{16}$ , along with  $7F_{16}$ , are known as **control characters**. For example, the ESC key on an ASCII keyboard generates a hex 1B code. The abbreviation ESC stands for extra services control but most people say "escape." The ESC character is often sent in combination with other characters to a peripheral device like a printer to turn on a special feature. Since such character sequences are not standardized, they will not be covered in this book.

The two ASCII control characters that will be used the most frequently in this book are  $0D_{16}$  and  $0A_{16}$ , for carriage return (CR) and line feed (LF). The  $0D_{16}$  code is generated by an ASCII keyboard when the Return or Enter key is pressed. When it is sent to an ASCII display, it causes the cursor to move to the beginning of the current line without going down to a new line. When carriage return is sent to an ASCII printer (at least one of older design), it causes the print head to move to the beginning of the line. The line feed code  $0A_{16}$  causes an ASCII display to move the cursor straight down, or a printer to roll the paper up one line, in both cases without going to the beginning of the new line. To display a message and move to the beginning of a new line, it is necessary to send the message characters plus CR and LF characters to the screen or printer. This may be annoying sometimes as you program in assembly language, but you will also have the option to not use CR and/or LF when you want to leave the cursor sor on a line after prompting for input, or to piece together a line using several output instructions.

Lesser-used control characters include form feed  $(0C_{16})$ , which causes many printers to eject a page; horizontal tab  $(09_{16})$ , which is generated by the tab key on the keyboard; backspace  $(08_{16})$  generated by the Backspace key; and delete  $(7F_{16})$  generated by the Delete key. Notice that the Backspace and Delete keys do not generate the same codes. The bell character  $(07_{16})$  causes an audible signal when output to the display. Good programming practice is to sound the bell only when really necessary.

Many large computers represent characters using Extended Binary Coded Decimal Information Code (abbreviated EBCDIC and pronounced ib-SEE-dick or eb-SEEdick). The EBCDIC system will only be used in this book as an example of another coding scheme when translation from one coding system to another is discussed.

#### Exercises 1.2

1. Each of the following hexadecimal numbers can be interpreted as representing a decimal number or a pair of ASCII codes. Give both interpretations.

(a) 2A45 (b) 7352 (c) 2036 (d) 106E

Find the ASCII codes for the characters in each of the following strings. Don't forget spaces and punctuation. Carriage return and line feed are shown by CR and LF, respectively (written together as CRLF so that it will be clear that there is no space character between them).

(a) January 1 is New Year's Day.CRLF

- (b) George said, "Ouch!"

- (c) R2D2 was C3P0's friend.CRLF ["0" is the numeral zero]

- (d) Your name? [put two spaces after the question mark]

- (e) Enter value: [put two spaces after the colon]

- 3. What would be displayed if you output each of the following sequences of ASCII codes to a computer's screen?

- (a) 62 6C 6F 6F 64 2C 20 73 77 65 61 74 20 61 6E 64 20 74 65 61 72 73

- (b) 6E 61 6D 65 0D 0A 61 64 64 72 65 73 73 0D 0A 63 69 74 79 0D 0A

- (c) 4A 75 6E 65 20 31 31 2C 20 31 39 34 37 0D 0A

- (d) 24 33 38 39 2E 34 35

- (e) 49 44 23 3A 20 20 31 32 33 2D 34 35 2D 36 37 38 39

#### **1.3** 2's Complement Representation for Signed Integers

It is now time to look more carefully at how numbers are actually represented in a computer. We have looked at two schemes to represent numbers—by using binary integers (often expressed in hex) or by using ASCII codes. However, these methods have two problems: (1) the number of bits available for representing a number is limited, and (2) it is not clear how to represent a negative number.

Chapter 2 will discuss computer hardware, but for now you need to know that memory is divided into **bytes**, each byte containing eight **bits**.<sup>2</sup> Suppose you want to use ASCII codes to represent a number in memory. A single ASCII code is normally stored in a byte. Recall that ASCII codes are seven bits long; the extra (left-hand, or high order) bit is set to 0. To solve the first representation problem mentioned above, you can simply include the code for a minus sign. For example, the ASCII codes for the four characters  $\pm$ 817 are 2D, 38, 31, and 37. To solve the first problem, you could always agree to use a fixed number of bytes, perhaps padding on the left with ASCII codes for zeros or spaces. Alternatively, you could use a variable number of bytes, but agree that the number ends with the last ASCII code for a digit, that is, terminating the string with a nondigit.

Suppose you want to use internal representations for numbers corresponding to their binary values. Then you must choose a fixed number of bits for the representation.

<sup>2</sup> Some early computer systems used byte sizes different than eight bits.

Most central processing units can do arithmetic on binary numbers having a few chosen lengths. For the Intel 80x86 family, these lengths are 8 bits (a byte), 16 bits (a **word**),<sup>3</sup> 32 bits (a **doubleword**), and 64 bits (a **quadword**).

As an example, look at the word-length binary representation of 697.

$697_{10} = 1010111001_2 = 0000001010111001_2$

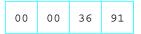

Leading zeros have been added to make 16 bits. Writing this in hex in a word, you have

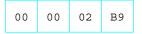

This illustrated convention will be followed throughout this book. Strips of boxes will represent sequences of bytes. The contents of a single byte will be represented in hex, with two hex digits in each byte since a single hex digit corresponds to four bits. The double-word representation of 697 simply has more leading zeros.

What we now have is a good system of representing nonnegative, or **unsigned**, numbers. This system cannot represent negative numbers. Also, for any given length, there is a largest unsigned number that can represented, for example  $FF_{16}$  or  $255_{10}$  for byte length.

As you have probably already guessed, the leftmost bit is always one in the 2'scomplement representation of a negative number. You might also guess that the rest of the representation is just the same as for the corresponding positive number, but unfor-

**<sup>3</sup>** Other computer architectures use a word size different than 16 bits.

tunately the situation is more complicated than that. That is, you *cannot* simply change the leading bit from 0 to 1 to get the negative version of a number.

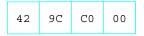

A hex calculator makes it easy to convert a negative decimal number to 2's complement form. For instance, if the decimal display shows  $\pm 565$  and the convert-to-hex key is pressed, a typical calculator will display FFFFFFDCB (perhaps with a different number of leading F's). For a word-size representation, ignore all but the last four hex digits; the answer is

or 1111 1101 1100 1011 in binary. (Note the leading 1 bit for a negative number.) The doubleword representation is

which is almost too long to write in binary.

The 2's complement representation of a negative number can also be found without a calculator. One method is to first express the unsigned number in hex, and then subtract this hex number from  $10000_{16}$  to get the word length representation. The number you subtract from is, in hex, a 1 followed by the number of 0's in the length of the representation; for example,  $10000000_{16}$  to get the doubleword length representation. (What would you use for a byte-length 2's complement representation?) For a quadword-length 2's complement representation?) In binary, the number of zeros is the length in binary digits. This binary number is a power of two, and subtraction is sometimes called "taking the complement," so this operation is the source of the term "2's complement."

#### Example

The word-length 2's complement representation of the decimal number  $\pm 76$  is found by first converting the unsigned number 76 to its hex equivalent 4C, then by subtracting 4C from 10000.

1 0 0 0 0 - 4 C Since you cannot subtract C from 0, you have to borrow 1 from 1000, leaving FFF.

$F F F ^{1}0$  - 4 C F F B 4

After borrowing, the subtraction is easy. The units digit is

$10_{16} \pm C_{16} = 16_{10} \pm 12_{10} = 4$  (in decimal or hex),

and the 16's position is

$F_{16} \pm 4 = 15_{10} \pm 4_{10} = 11_{10} = B_{16}$

It is not necessary to convert the hex digits to decimal to subtract them if you learn the addition and subtraction tables for single hex digits.

The operation of subtracting a number from 1 followed by an appropriate number of 0's is called **taking the 2's complement**, or complementing the number. Thus "2's complement" is used both as the name of a representation system and as the name of an operation. The operation of taking the 2's complement corresponds to pressing the change sign key on a hex calculator.

Since a given 2's complement representation is a fixed length, obviously there is a maximum size number that can be stored in it. For a word, the largest positive number stored is 7FFF, since this is the largest 16 bit long number that has a high order bit of 0 when written in binary. The hex number 7FFF is 32767 in decimal. Positive numbers written in hex can be identified by a leading hex digit of 0 through 7. Negative numbers are distinguished by a leading bit of 1, corresponding to hex digits of 8 through F.

How do you convert a 2's complement representation to the corresponding decimal number? First, determine the sign of a 2's complement number. To convert a positive 2's complement number to decimal, just treat it like any unsigned binary number and convert it by hand or with a hex calculator. For example, the word-length 2's complement number 0D43 represents the decimal number 3395.

Dealing with a negative 2's complement number—one starting with a 1 bit or 8 through F in hex—is a little more complicated. Note that any time you take the 2's com-

plement of a number and then take the 2's complement of the result, you get back to the original number. For a word size number N, ordinary algebra gives you

$N = 10000 \pm (10000 \pm N)$

For example, using the word length 2's complement value F39E

$10000 \pm (10000 \pm F39E) = 10000 \pm C62 = F39E$

This says again that the 2's complement operation corresponds to negation. Because of this, if you start with a bit pattern representing a negative number, the 2's complement operation can be used to find the positive (unsigned) number corresponding it.

#### Example

The word-length 2's complement number E973 represents a negative value since the sign bit (leading bit) is 1 (E = 1110). Taking the complement finds the corresponding positive number.

$10000 \pm E973 = 168D = 5773_{10}$

This means that the decimal number represented by E973 is  $\pm 5773$ .

The word-length 2's complement representations with a leading 1 bit range from 8000 to FFFF. These convert to decimal as follows:

$10000 \pm 8000 = 8000 = 32768_{10}$

so 8000 is the representation of  $\pm$  32768. Similarly,

$10000 \pm FFFF = 1,$

so FFFF is the representation of  $\pm 1$ . Recall that the largest positive decimal integer that can be represented as a word-length 2's complement number is 32767; the range of decimal numbers that can be represented in word-length 2's complement form is  $\pm 32768$  to 32767.

Using a calculator to convert a negative 2's complement representation to a decimal number is a little tricky. For example, if you start with the word length representation FF30 and your calculator displays 10 hex digits, you must enter the 10 hex digit

long version of the number FFFFFFF30, with six extra leading F's. Then push the convert to decimal button(s) and your calculator should display  $\pm 208$ .

#### Exercises 1.3

- 1. Find the word-length 2's complement representation of each of the following decimal numbers:

- (a) 845

- (b) 15000

- (c) 100

- (d)  $\pm 10$

- (e)  $\pm 923$

- 2. Find the doubleword-length 2's complement representation of each of the following decimal numbers:

- (a) 3874

- (b) 1000000

- (c) ±100

- (d) ±55555

- 3. Find the byte-length 2's complement representation of each of the following decimal numbers:

- (a) 23

- (b) 111

- (c) ±100

- (d) ±55

- 4. Find the decimal integer that is represented by each of these wordlength 2's complement numbers:

- (a) 00 A3

- (b) FF FE

- (c) 6F 20

- (d) B6 4A

- 5. Find the decimal integer that is represented by each of these doubleword-length 2's complement numbers:

- (a) 00 00 F3 E1

- (b) FF FF FE 03

- (c) 98 C2 41 7D

- 6. Find the decimal integer that is represented by each of these bytelength 2's complement numbers:

- (a) E1

- (b) 7C

- (c) FF

- 7. Find the range of decimal integers that can be stored in 2's complement form in a byte.

- 8. Find the range of decimal integers that can be stored in 2's complement form in a doubleword.

- 9. This section showed how to take the 2's complement of a number by subtracting it from an appropriate power of 2. An alternative method is to write the number in binary (using the correct number of bits for the length of the representation), change each 0 bit to 1 and each 1 bit to zero (this is called "taking the 1's complement"), and then adding 1 to the result (discarding any carry into an extra bit). Show that these two methods are equivalent.

### 1.4 Addition and Subtraction of 2's Complement Numbers

One of the reasons that the 2's complement representation scheme is commonly used to store signed integers in computers is that addition and subtraction operations can be easily and efficiently implemented in computer hardware. This section discusses addition and subtraction of 2's complement numbers and introduces the concepts of carry and overflow that will be needed later.

To add two 2's complement numbers, simply add them as if they were unsigned binary numbers. The 80x86 architecture uses the same addition instructions for unsigned and signed numbers. The following examples use word-size representations.

First, 0A07 and 01D3 are added. These numbers are positive whether they are interpreted as unsigned numbers or as 2's complement numbers. The decimal version of the addition problem is given on the right.

| 0A07          | 2567  |

|---------------|-------|

| + <u>01D3</u> | + 467 |

| 0BDA          | 3034  |

The answer is correct in this case since  $BDA_{16} = 3034_{10}$ .

Next, 0206 and FFB0 are added. These are, of course, positive as unsigned numbers, but interpreted as 2's complement signed numbers, 0206 is a positive number and FFB0 is negative. This means that there are two decimal versions of the addition problem. The signed one is given first, then the unsigned version.

| 518            | 518     | 0206          |

|----------------|---------|---------------|

| + <u>65456</u> | + (-80) | + <u>FFB0</u> |

| 65974          | 438     | 101B6         |

There certainly appears to be a problem since it will not even fit in a word. In fact, since 101B6 is the hex version of 65974, there is no way to represent the correct sum of unsigned numbers in a word. However, if the numbers are interpreted as signed and you ignore the extra 1 on the left, then the word 01B6 is the 2's complement representation of the decimal number 438.

Now FFE7 and FFF6 are added, both negative numbers in a signed interpretation. Again, both signed and unsigned decimal interpretations are shown.

| FFE7          | (-25)   | 65511          |

|---------------|---------|----------------|

| + <u>FFF6</u> | + (-10) | + <u>65526</u> |

| 1FFDD         | -35     | 131037         |

Again, the sum in hex is too large to fit in two bytes, but if you throw away the extra 1, then FFDD is the correct word-length 2's complement representation of  $\pm 35$ .

Each of the last two additions have a **carry** out of the usual high order position into an extra digit. The remaining digits give the correct 2's complement representation. The remaining digits are not always the correct 2's complement sum, however. Consider the addition of the following two positive numbers:

|   | 483F        |   |   | 18495        |

|---|-------------|---|---|--------------|

| + | <u>645A</u> | + | - | <u>25690</u> |

|   | AC99        |   |   | 44185        |

There was no carry out of the high order digit, but the signed interpretation is plainly incorrect since AC99 represents the *negative* number  $\pm 21351$ . Intuitively, what went wrong is that the decimal sum 44185 is bigger than the maximal value 32767 that can be stored in the two bytes of a word. However, when these numbers are interpreted as unsigned, the sum is correct.

The following is another example showing a "wrong" answer, this time resulting from adding two numbers that are negative in their signed interpretation.

| E9FF          | (-5633)    | 59903          |

|---------------|------------|----------------|

| + <u>8CF0</u> | + (-29456) | + <u>36080</u> |

| 176EF         | -35089     | 95983          |

This time there is a carry, but the remaining four digits 76 EF cannot be the right-signed answer since they represent the *positive* number 30447. Again, intuition tells you that something had to go wrong since  $\pm 32768$  is the most negative number that can be stored in a word.

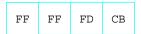

In the above "incorrect" examples, **overflow** occurred. As a human being, you detect overflow by the incorrect signed answer. Computer hardware can detect overflow as it performs addition, and the signed sum will be correct if there is no overflow. The computer actually performs addition in binary, of course, and the process is logically a right-to-left pairwise addition of bits, very similar to the procedure that humans use for decimal addition. As the computer adds a pair of bits, sometimes a carry (of 1) into the next column to the left is generated. This carry is added to the sum of these two bits, etc. The column of particular interest is the leftmost one: the sign position. There may be a carry *into* this position and/or a carry *out of* this position into the "extra" bit. This "carry out" (into the extra bit) is what was called just "carry" above and was seen as the extra hex 1. Figure 1.2 identifies when overflow does or does not occur. The table can be summarized by saying that overflow occurs when the number of carries into the sign position is different from the number of carries out of the sign position.

Each of the above addition examples is now shown again, this time in binary. Carries are written above the two numbers.

| Carry into sign bit? | Carry out of sign bit? | Overflow? |  |

|----------------------|------------------------|-----------|--|

| no                   | no                     | no        |  |

| no                   | yes                    | yes       |  |

| yes                  | no                     | yes       |  |

| yes                  | yes                    | no        |  |

|                      |                        |           |  |

|   |      |      |      | 111  |   |             |

|---|------|------|------|------|---|-------------|

|   | 0000 | 1010 | 0000 | 0111 |   | 0A07        |

| + | 0000 | 0001 | 1101 | 0011 | + | <u>01D3</u> |

|   | 0000 | 1011 | 1101 | 1010 |   | 0BDA        |

This example has no carry into the sign position and no carry out, so there is no overflow.

|               |      |      | 11   | 1111        | 1 |

|---------------|------|------|------|-------------|---|

| 0206          | 0110 | 0000 | 0010 | 0000        |   |

| + <u>FFB0</u> | 0000 | 1011 | 1111 | <u>1111</u> | + |

| 101B6         | 0110 | 1011 | 0001 | 0000        | 1 |

This example has a carry into the sign position and a carry out, so there is no overflow.

| 1 | 1111        | 1111 | 11   | 11   |               |

|---|-------------|------|------|------|---------------|

|   | 1111        | 1111 | 1110 | 0111 | FFE7          |

| + | <u>1111</u> | 1111 | 1111 | 0110 | + <u>FFF6</u> |

| 1 | 1111        | 1111 | 1101 | 1101 | 1FFDD         |

Again, there is both a carry into the sign position and a carry out, so there is no overflow.

|   | 1    |      | 1111 | 11   |   |   |             |

|---|------|------|------|------|---|---|-------------|

|   | 0100 | 1000 | 0011 | 1111 |   |   | 483F        |

| + | 0110 | 0100 | 0101 | 1010 | + | - | <u>645A</u> |

|   | 1010 | 1100 | 1001 | 1001 |   |   | AC99        |

Overflow does occur in this addition since there is a carry into the sign position, but no carry out.

| 1 | 1    | 11   | 111  |      |               |

|---|------|------|------|------|---------------|

|   | 1110 | 1001 | 1111 | 1111 | E9FF          |

| + | 1000 | 1100 | 1111 | 0000 | + <u>8CF0</u> |

| 1 | 0111 | 0110 | 1110 | 1111 | 176EF         |

There is also overflow in this addition since there is a carry out of the sign bit, but no carry in.

In a computer, subtraction  $a \pm b$  of numbers a and b is usually performed by taking the 2's complement of b and adding the result to a. This corresponds to adding the negation of b. For example, for the decimal subtraction  $195 \pm 618 = \pm 423$ ,

00C3

± 026A

is changed to addition of FD96, the 2's complement of 026A.

00C3 + <u>FD96</u> FE59

The hex digits FE59 do represent  $\pm 423$ . Looking at the above addition in binary, you have

11 11 0000 0000 1100 0011 + <u>1111 1101 1001 0110</u> 1111 1110 0101 1001

Notice that there was no carry in the addition. However, this subtraction did involve a **borrow**. A borrow occurs in the subtraction  $a \pm b$  when b is larger than a as unsigned numbers. Computer hardware can detect a borrow in subtraction by looking at whether on not a carry occurred in the corresponding addition. If there is no carry in the addition, then there is a borrow in the subtraction. If there is a carry in the addition, then there is no borrow in the subtraction. (Remember that "carry" by itself means "carry out.")

Here is one more example. Doing the decimal subtraction 985  $\pm$  411 = 574 using word-length 2's complement representations,

03D9 - 019B

is changed to addition of FE65, the 2's complement of 019B.

|               | 1 | 1111        | 1111 | 1    | 1    |

|---------------|---|-------------|------|------|------|

| 03D9          |   | 0000        | 0011 | 1101 | 1001 |

| + <u>FE65</u> | + | <u>1111</u> | 1110 | 0110 | 0101 |

| 1023E         | 1 | 0000        | 0010 | 0011 | 1110 |

Discarding the extra 1, the hex digits 023E do represent 574. This addition has a carry, so there is no borrow in the corresponding subtraction.

Overflow is also defined for subtraction. When you are thinking like a person, you can detect it by the wrong answer that you will expect when you know that the difference is going to be outside of the range that can be represented in the chosen length for the representation. A computer detects overflow in subtraction by determining whether or not overflow occurs in the corresponding addition problem. If overflow occurs in the addition problem, then it occurs in the original subtraction problem; if it does not occur in the addition, then it does not occur in the original subtraction. There was no overflow in either of the above subtraction examples. Overflow does occur if you use word-length 2's complement representations to attempt the subtraction  $\pm 29123 \pm 15447$ . As a human, you know that the correct answer  $\pm 44570$  is outside the range  $\pm 32,768$  to +32,767. In the computer hardware

8E3D

- 3C57

is changed to addition of C3A9, the 2's complement of 3C57.

|               | 1 | 1           | 11   | 111  | 1    |

|---------------|---|-------------|------|------|------|

| 8E3D          |   | 1000        | 1110 | 0011 | 1101 |

| + <u>C3A9</u> | + | <u>1100</u> | 0011 | 1010 | 1001 |

| 151E6         | 1 | 0101        | 0001 | 1110 | 0110 |

There is a carry out of the sign position, but no carry in, so overflow occurs.

Although examples in this section have use word-size 2's complement representations, the same techniques apply when performing addition or subtraction with byte-size, doubleword-size, or other size 2's complement numbers.

#### Exercises 1.4

Perform each of the following operations on word-size 2's complement numbers. For each, find the specified sum or difference. Determine whether overflow occurs. For a sum, determine whether there is a carry. For a difference, determine whether there is a borrow. Check your answers by converting the problem to decimal.

- 1. 003F + 02A4 2. 1B48 + 39E1

- 3. 6C34 + 5028 4. 7FFE + 0002

- 5. FF07 + 06BD 6. 2A44 + D9CC

| 7.  | FFE3 + FC70                 | 8.  | FE00 + FD2D                   |

|-----|-----------------------------|-----|-------------------------------|

| 9.  | FFF1 + 8005                 | 10. | 8AD0 + EC78                   |

| 11. | $9E58 \pm EBBC$             | 12. | $\text{EBBC} \pm 9\text{E58}$ |

| 13. | $\text{EBBC}\pm791\text{C}$ | 14. | $791C \pm EBBC$               |

#### 1.5 Other Systems for Representing Numbers

Sections 1.2 and 1.3 presented two commonly-used systems for representing numbers in computers, strings of character codes (often ASCII), and 2's complement form. This section introduces three additional schemes, 1's complement, binary coded decimal (BCD), and floating point. The 1's complement system is an alternative scheme for representing signed integers; it is used in a few computer systems, but not the Intel 80x86 family. Binary coded decimal and floating point forms are used in 80x86 computers, as well as many other systems. They will be discussed more fully when appropriate instructions for manipulating data in these forms are covered. The primary reason for introducing them here is to illustrate that there are many alternative representations for numeric data, each valid when used in the correct context.

The **1's complement** system is similar to 2's complement. A fixed length is chosen for the representation and a positive integer is simply the binary form of the number, padded with one or more leading zeros on the left to get the desired length. To take the negative of the number, each bit is "complemented"; that is, each zero is changed to one and each one is changed to zero. This operation is sometimes referred to as taking the 1's complement of a number. Although it is easier to negate an integer using 1's complement than 2's complement, the 1's complement system has several disadvantages, the most significant being that it is harder to design circuitry to add or subtract numbers in this form. There are two representations for zero (why?), an awkward situation. Also, a slightly smaller range of values can be represented; for example,  $\pm 127$  to 127 for an 8 bit length, instead of  $\pm 128$  to 127 in a 2's complement system.

The byte length 1's complement representation of the decimal number 97 is just the value 0110 0001 in binary (61 in hex). Changing each 0 to 1 and each 1 to 0 gives 1001 1110 (9E in hex), the byte length 1's complement representation of  $\pm$ 97.

There is a useful connection between taking the 1's complement and taking the 2's complement of a binary number. If you take the 1's complement of a number and then add 1, you get the 2's complement. This is sometimes easier to do by hand than the

subtraction method presented in Section 1.3. You were asked to verify the equivalence of these methods in Exercise 1.3.9.

In **binary coded decimal** (BCD) schemes, each decimal digit is coded with a string of bits with fixed length, and these strings are pieced together to form the representation. Most frequently four bits are used for each decimal digit; the choices for bit patterns are shown in Fig. 1.3. Only these ten bit patterns are used.

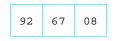

One BCD representation of the decimal number 926708 is 1001 0010 0110 0111 0000 1000. Using one hex digit as shorthand for four bits, and grouping two hex digits per byte, this BCD representation can be expressed in three bytes as

Notice that the BCD representation in hex looks just like the decimal number.

Often BCD numbers are encoded using some fixed number of bytes. For purposes of illustration, assume a four-byte representation. For now, the question of how to represent a sign will be ignored; without leaving room for a sign, eight binary-coded decimal digits can be stored in four bytes. Given these choices, the decimal number 3691 has the BCD representation

| BCD bit pattern |

|-----------------|

| 0000            |

| 0001            |

| 0010            |

| 0011            |

| 0100            |

| 0101            |

| 0110            |

| 0111            |

| 1000            |

| 1001            |

|                 |

Figure 1.3 Binary coded decimal representation

Notice that the doubleword 2's complement representation for the same number would be 00 00 0E 6B, and that the ASCII codes for the four numerals are 33 36 39 31.

It is not as efficient for a computer to do arithmetic with numbers in a BCD format as with 2's complement numbers. It is usually very inefficient to do arithmetic on numbers represented using ASCII codes. However, ASCII codes are the only method so far for representing a number that is not an integer. For example, 78.375 can be stored as 37 38 2E 33 37 35. Floating point representation systems allow for nonintegers to be represented, or at least closely approximated.

Floating point schemes store numbers in a form that corresponds closely to scientific notation. The following example shows how to convert the decimal number 78.375 into IEEE single format that is 32 bits long. (IEEE is the abbreviation for the Institute of Electrical and Electronics Engineers.) This format was one of several sponsored by the Standards Committee of the IEEE Computer Society and approved by the IEEE Standards Board and the American National Standards Institute (ANSI). It is one of the floating point formats used in Intel 80x86 processors.

First, 78.375 must be converted to binary. In binary, the positions to the right of the binary point (it is not appropriate to say *decimal* point for the "." in a binary number) correspond to negative powers of two (1/2, 1/4, 1/8, etc.), just as they correspond to negative powers of 10 (1/10, 1/100, etc.) in a decimal number. Since  $0.375 = 3/8 = 1/4 + 1/8 = .01_2 + .001_2$ ,  $0.375_{10} = 0.011_2$ . The whole part 78 is 1001110 in binary, so

$78.375_{10} = 1001110.011_2.$

Next this is expressed in binary scientific notation with the mantissa written with 1 before the radix point.

$$1001110.011_2 = 1.001110011 \pi 2^6$$

The exponent is found exactly as it is in decimal scientific notation, by counting the number of positions the point must be moved to the right or left to produce the mantissa. The notation here is really mixed; it would be more proper to write 2<sup>6</sup> as 10<sup>110</sup>, but it is more convenient to use the decimal form. Now the floating point number can be pieced together:

- left bit 0 for a positive number (1 means negative)

- 1000 0101 for the exponent. This is the actual exponent of 6, plus a **bias** of 127, with the sum, 133, in 8 bits.

This example worked out easily because 0.375, the noninteger part of the decimal number 78.375, is a sum of negative powers of 2. Most numbers are not as nice, and usually a binary fraction is chosen to closely approximate the decimal fraction. Techniques for choosing such an approximation are not covered in this book.

To summarize, the following steps are used to convert a decimal number to IEEE single format:

- The leading bit of the floating point format is 0 for a positive number and 1 for a negative number.

- 2. Write the unsigned number in binary.

- 3. Write the binary number in binary scientific notation  $f_{23}$ . $f_{22}$ ... $f_0 \pi 2^e$ , where  $f_{23} = 1$ . There are 24 fraction bits, but it is not necessary to write trailing 0's.

- Add a bias of 127<sub>10</sub> to the exponent e. This sum, in binary form, is the next 8 bits of the answer, following the sign bit. (Adding a bias is an alternative to storing the exponent as a signed number.)

- 5. The fraction bits  $f_{22}f_{21} \dots f_0$  form the last 23 bits of the floating point number. The leading bit  $f_{23}$  (which is always 1) is dropped.

Computer arithmetic on floating point numbers is usually much slower than with 2's complement integers. However the advantages of being able to represent nonintegral values or very large or small values often outweigh the relative inefficiency of computing with them.

### **Exercises 1.5**

Express each of the following decimal numbers as a word-length 1's complement number.

| 1. | 175 | 2. | $\pm 175$ |

|----|-----|----|-----------|

|    |     |    |           |

3. ±43 4. 43

Use BCD to encode each of the following decimal numbers in four bytes. Express each answer in hex digits, grouped two per byte.

- 5. 230 6. 1

- 7. 12348765 8. 17195

Use IEEE single format to encode each of the following decimal numbers in floating point.

- 9. 175.5 10. ±1.25

- 11. ±11.75 12. 45.5

# **Chapter Summary**

All data are represented in a computer using electronic signals. These can be interpreted as patterns of binary digits (bits). These bit patterns can be thought of as binary numbers. Numbers can be written in decimal, hexadecimal, or binary forms.

For representing characters, most microcomputers use ASCII codes. One code is assigned for each character, including nonprintable control characters.

Integer values are represented in a predetermined number of bits in 2's complement form; a positive number is stored as a binary number (with at least one leading zero to make the required length), and the pattern for a negative number can be obtained by subtracting the positive form from a 1 followed by as many 0's as are used in the length. A 2's complement negative number always has a leading 1 bit. A hex calculator, used with care, can simplify working with 2's complement numbers.

Addition and subtraction are easy with 2's complement numbers. Since the length of a 2's complement number is limited, there is the possibility of a carry, a borrow, or overflow.

Other formats in which numbers are stored are 1's complement, binary coded decimal (BCD), and floating point.

# CHAPTER 2

# Parts of a Computer System

A practical computer system consists of hardware and software. The major hardware components of a typical microcomputer system are a central processing unit (CPU), memory circuits, a keyboard for input, a monitor or some other display device, specialized input/output devices like a mouse, a modem, or a sound card, and one or more disk drives to store programs and data. Software refers to the programs that the hardware executes, including system software and application software.

These basic components vary from one computer system to another. This chapter discusses how the memory and CPU look to the assembly language programmer for a particular class of microcomputers, the IBM PC and compatible systems. These computers have an Intel 80x86 CPU; that is, an 8086 or 8088, an 80286, an 80386, an 80486, or a Pentium processor.<sup>1</sup> This book assumes a system that has an 80386 or higher processor and a 32-bit operating system such as Windows 95 or Windows NT. The remainder of the book is concerned with using assembly language to program these systems, with the intent of showing how such systems work at the hardware level.

- 2.2

- 2.3

- **2.4** PC software

2.1

<sup>1</sup> Intel produced an 80186 CPU, but it was rarely used in commercial microcomputers.

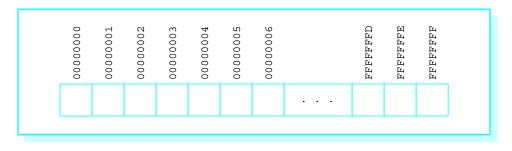

# 2.1 PC Hardware: Memory

The memory in an IBM PC or compatible microcomputer is logically a collection of "slots," each of which can store one byte of instructions or data. Each memory byte has a 32-bit numeric label called its **physical address**. A physical address can always be expressed as eight hex digits. The first address is  $00000000_{16}$  and the last address can be as large as the unsigned number FFFFFFF<sub>16</sub>. Figure 2.1 shows a logical picture of the possible memory in a PC. Since FFFFFFF<sub>16</sub> = 4,294,967,295, a PC can contain up to 4,294,967,296 bytes of memory, or four gigabytes. In practice, the user memory in most PCs is smaller than this.

Figure 2.1 Logical picture of PC memory

Prior to the 80386 chip, the Intel 80x86 family of processors could only directly address 2<sup>20</sup> bytes of memory. They used 20-bit physical addresses, often expressed as 5-hex-digit addresses ranging from 00000 to FFFFF.

Physically a PC's memory consists of integrated circuits (ICs). Many of these chips provide **random access memory** (**RAM**), which can be written to or read from by program instructions. The contents of RAM chips are lost when the computer's power is turned off. Other ICs are **read-only memory** (**ROM**) chips, which permanently retain their contents and can be read from but not written to.

The assembly language programs in this book will use a **flat memory** model. This means that the programs will actually encode 32-bit addresses to logically reference locations in a single memory space where data and instructions are stored.

The Intel 80x86 architecture also provides for a **segmented memory** model. In the original 8086/8088 CPU, this memory model was the only one available. With the 8086/8088, the PC's memory is visualized as a collection of segments, each segment 64 Kbytes long, starting on an address that is a multiple of 16. This means that one segment starts at address 00000, another (overlapping the first) starts at address 16  $(00010_{16})$ , another starts at address 32  $(00020_{16})$ , etc. Notice that the starting address of a segment ends in 0 when written in hex. The **segment number** of a segment consists of the first four hex digits of its physical address.

A program written for the 8086/8088 does not encode a five-hex-digit address. Instead, each memory reference depends on its segment number and a 16-bit **offset** from the beginning of the segment. Normally only the offset is encoded, and the segment number is deduced from context. The offset is the distance from the first byte of the segment to the byte being addressed. In hex, an offset is between 0000 and  $\text{FFFF}_{16}$ . The notation for a segment-offset address is the four-hex-digit segment number followed by a colon (:) followed by the four-hex-digit offset.

As an example, 18A3:5B27 refers to the byte that is 5B27 bytes from the beginning of the segment starting at address 18A30. Add the starting address and the offset to get the five-hex-digit address.

| 18A30         | starting  | address  | of   | segment | 18A3 |

|---------------|-----------|----------|------|---------|------|

| + <u>5B27</u> | offset    |          |      |         |      |

| 1E557         | five-hex- | digit ad | ddre | ess     |      |

From the 80386 on, 80x86 processors have had both 16-bit and 32-bit segmented memory models available. Segment numbers are still 16-bits long, but they do not directly reference a segment in memory. Instead, a segment number is used as an index into a table that contains the actual 32-bit starting address of the segment. In the 32-bit segmented model, a 32-bit offset is added to that starting address to compute the actual address of the memory operand. Segments can be logically useful to a programmer: In the segmented Intel model, the programmer normally assigns different memory segments to code, data, and a system stack. The 80x86 flat memory model is really a 32bit segmented model with all segment registers containing the same value.

In reality, the 32-bit address generated by a program is not necessarily the physical address at which an operand is stored as the program executes. There is an additional layer of memory management performed by the operating system and the Intel 80x86 CPU. A **paging** mechanism is used to map the program's 32-bit addresses into physical addresses. Paging is useful when a logical address generated by a program exceeds the physical memory actually installed in a computer. It can also be used to swap parts of a program from disk as needed when the program is too large to fit into physical memory. The paging mechanism will be transparent to us as we program in assembly language.

### Exercises 2.1

- 1. Suppose that you buy a PC with 32 MBytes of RAM. What is the 8-hexdigit address of the "last" byte?

- 2. Suppose that you discover that RAM addresses 000C0000 to 000C7FFF are reserved for a PC's video adapter. How many bytes of memory is this?

- 3. Suppose that you have an Intel 8086. Find the five-hex-digit address that corresponds to each of these segment:offset pairs:

(a) 2B8C:8D21 (b) 059A:7A04 (c) 1234:5678

# 2.2 PC Hardware: The CPU

The original 8086/8088 CPU could execute over 200 different instructions. This instruction set has been extended as the 80x86 processor family has expanded to include the 80286, 80386, 80486, and Pentium processors. Much of this book will be concerned with using these instructions to implement programs so that you understand the machinelevel computer capabilities. Other manufacturers make CPUs that execute essentially the same instruction set, so that a program written for an Intel 80x86 runs without change on such CPUs. Many other processor families execute different instruction sets. However, most have a similar architecture, so that the basic principles you learn about the 80x86 CPUs also apply to these systems.

A CPU contains **registers**, each an internal storage location that can be accessed much more rapidly than a location in RAM. The application registers are of most concern to the programmer. An 80x86 CPU (from 80386 on) has 16 application registers. Typical instructions transfer data between these registers and memory or perform operations on data stored in the registers or in memory. All of these registers have names, and some of them have special purposes. Their names are given below and some of their special purposes are described. You will learn more special purposes later.

The EAX, EBX, ECX, and EDX registers are called **data registers** or **general reg**isters. The EAX register is sometimes known as the **accumulator** since it is the destination for many arithmetic results. An example of an instruction using the EAX register is

### add eax, 158

which adds the decimal number 158 (converted to doubleword length 2's complement form) to the number already in EAX, replacing the number originally in EAX by the sum.

(Full descriptions of the add instruction and others mentioned below will appear in Chapter 4.)

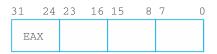

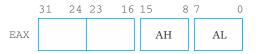

Each of EAX, EBX, ECX, and EDX is 32 bits long. The Intel convention is to number bits right to left starting with 0 for the low-order bit, so that if you view one of these registers as four bytes, then the bits are numbered like this

Parts of the EAX register can be addressed separately from the whole. The low-order word, bits 0-15, is known as AX.

The instruction

sub ax, 10

subtracts 10 from the word stored in AX, without changing any of the high-order bits (16–31) of EAX.

Similarly, the low-order byte (bits 0–7) and the high-order byte (bits 8–15) of AX are known as AL and AH, respectively.

The instruction

mov ah, '\*'

copies 2A, the ASCII code for an asterisk, to bits 8–15, without changing any of the other bits of EAX.

The EBX, ECX, and EDX registers also have low-order words BX, CX, and DX, which are divided into high-order and low-order bytes BH and BL, CH and CL, and DH and DL. Each of these parts can be changed without altering other bits. It may be a surprise that there are *no* comparable names for the high-order words in EAX, EBX, ECX, and EDX—you cannot reference bits 16–31 independently by name.

The 8086 through 80286 processors had four 16-bit general registers called AX, BX, CX, and DX. The "E" was added for "extended" with the 32-bit 80386 registers. However, the 80386 and later architectures effectively include the older 16-bit architecture.

There are four additional 32-bit registers that Intel also calls general, ESI, EDI, ESP, and EBP. In fact, you can use these registers for operations like arithmetic, but normally you should save them for their special purposes. The ESI and EDI registers are **index registers**, where SI stands for source index and DI stands for destination index. One of their uses is to indicate memory addresses of the source and destination when strings of characters are moved from one place to another in memory. They can also be used to implement array indexes. The names SI and DI can be used for the low-order words of ESI and EDI, respectively, but we will have little occasion to do this.

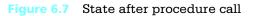

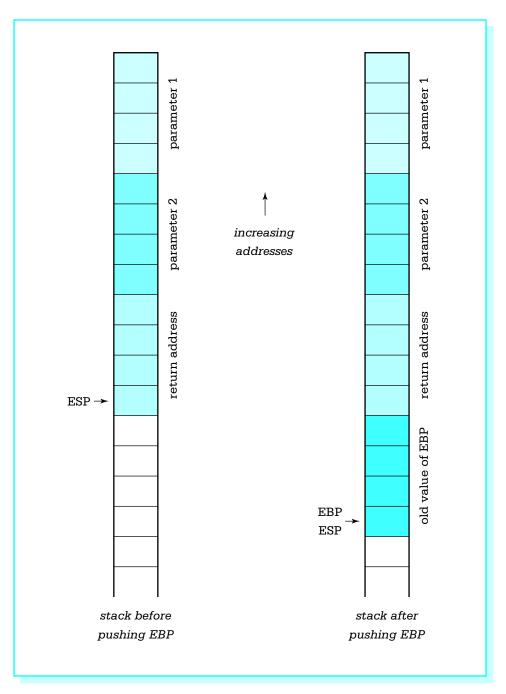

The ESP register is the **stack pointer** for the system stack. It is rarely changed directly by a program, but is changed when data is pushed onto the stack or popped from the stack. One use for the stack is in procedure (subroutine) calls. The address of the instruction following the procedure call instruction is stored on the stack. When it is time to return, this address is retrieved from the stack. You will learn much more about the stack and the stack pointer register in Chapter 6. The name SP can be used for the low-order word of ESP, but this will not be done in this book.

The EBP register is the **base pointer** register. Normally the only data item accessed in the stack is the one that is at the top of the stack. However, the EBP register is often used to mark a fixed point in the stack other than the stack top, so that data near this point can be accessed. This is also used with procedure calls, particularly when parameters are involved.

There are six 16-bit **segment registers**: CS, DS, ES, FS, GS, and SS. In the older 16-bit segmented memory model, the CS register contains the segment number of the code segment, the area of memory where the instructions currently being executed are stored. Since a segment is 64K long, the length of a program's collection of instructions is often limited to 64K; a longer program requires that the contents of CS be changed while the program is running. Similarly DS contains the segment number of the data segment, the area

of memory where most data is stored. The SS register contains the segment number of the stack segment, where the stack is maintained. The ES register contains the segment number of the extra data segment that could have multiple uses. The FS and GS registers were added with the 80386 and make possible easy access to two additional data segments.

With the flat 32-bit memory model we will use, the segment registers become essentially irrelevant to the programmer. The operating system will give each of CS, DS, ES, and SS the same value. Recall that this is a pointer to table entry that includes the actual starting address of the segment. That table also includes the size of your program, so that the operating system can indicate an error if your program accidentally or deliberately attempts to write in another area. However, all of this is transparent to the programmer who can just think in terms of 32-bit addresses.

The 32-bit **instruction pointer**, or EIP register, cannot be directly accessed by an assembly language programmer. The CPU has to fetch instructions to be executed from memory, and EIP keeps track of the address of the next instruction to be fetched. If this were a older, simpler computer architecture, the next instruction to be fetched would also be the next instruction to be executed. However, an 80x86 CPU actually fetches instructions to be executed later while it is still executing prior instructions, making the assumption (usually correct) that the instructions to be executed next will follow sequentially in memory. If this assumption turns out to be wrong, for example if a procedure call is executed, then the CPU throws out the instructions it has stored, sets EIP to contain the offset of the procedure, and then fetches its next instruction from the new address.

In addition to prefetching instructions, an 80x86 CPU actually starts execution of an instruction before it finishes execution of prior instructions. This use of **pipelining** increases effective processor speed.

The final register is called the **flags register**. The name EFLAGS refers to this register, but this mnemonic is not used in instructions. Some of its 32 bits are used to set some characteristic of the 80x86 processor. Other bits, called **status flags**, indicate the outcome of execution of an instruction. Some of the flag register's 32 bits are named, and the names we will use most frequently are given in Fig. 2.2.

Bit 11 is the overflow flag (OF). It is set to 0 following an addition in which no overflow occurred, and to 1 if overflow did occur. Similarly, bit 0, the carry flag (CF), indicates the absence or presence of a carry out from the sign position after an addition. Bit 7, the sign flag, contains the left bit of the result after some operations. Since the left bit is 0 for a nonnegative two's complement number and 1 for a negative number, SF indicates the sign. Bit 6, the zero flag (ZF) is set to 1 if the result of some operation is zero,

| Bit | Mnemonic | Usage          |

|-----|----------|----------------|

| 0   | CF       | carry flag     |

| 2   | PF       | parity flag    |

| 6   | ZF       | zero flag      |

| 7   | SF       | sign flag      |

| 10  | DF       | direction flag |

| 11  | OF       | overflow flag  |

|     |          |                |

Figure 2.2 Selected EFLAGS bits

and to 0 if the result is nonzero (positive or negative). Bit 2, the parity flag, is set to 1 if the number of 1 bits in a result is even and to 0 if the number of 1 bits in the result is odd. Other flags will be described later when their uses will be clearer.

As an example of how flags are set by instructions, consider again the instruction

add eax, 158

This instruction affects CF, OF, PF, SF, and ZF. Suppose that EAX contains the word FF FF FF F3 prior to execution of the instruction. Since  $158_{10}$  corresponds to the word 00 00 00 9E, this instruction adds FF FF F3 and 00 00 00 9E, putting the sum 00 00 00 91 in the EAX register. It sets the carry flag CF to 1 since there is a carry, the overflow flag OF to 0 since there is no overflow, the sign flag SF to 0 (the leftmost bit of the sum 00 00 00 00 91), and the zero flag ZF to 0 since the sum is not zero. The parity flag PF is set to 0 since 0000 0000 0000 0000 0000 1001 0001 contains three 1 bits, an odd number.

In summary, the 80x86 CPU executes a variety of instructions, using its 16 internal registers for operands and results of operations, and for keeping track of segment selectors and addresses. The registers are summarized in Fig. 2.3.

### Exercises 2.2

For each add instruction below, assume that EAX contains the given contents before the instruction is executed, and give the contents of EAX as well as the values of the CF, OF, SF, and ZF flags after the instruction is executed:

| Name   | Length (bits) | Use/comments                                                      |

|--------|---------------|-------------------------------------------------------------------|

| EAX    | 32            | accumulator, general use;                                         |

|        |               | low-order-word AX, divided into bytes AH and AL                   |

| EBX    | 32            | general use;                                                      |

|        |               | low-order-word BX, divided into bytes BH and BL                   |

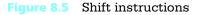

| ECX    | 32            | general use;                                                      |