"Adrian knows more about tweaking a BIOS than Bill Gates knows about Windows!" —DIGITAL DAVE, WINOSCENTRAL.COM

# **Breaking Through**

# DIU5 Barrier

The Definitive BIOS Optimization Guide for PCs

Adrian Wong

"Adrian has done the tech community a great service by making this guide. It has personally saved me time on both repairs and evaluations. With BIOS options as numerous as they are today, it's wonderful to have a one-stop-source to decipher them all."

#### -Nathan Warawa, GamingIn3D.com

"You know, I couldn't count the amount of times I've referred people to your BIOS Guide...it's very informative, and saves me the time of explaining why people should disable Video BIOS Shadowing, why FastWrites isn't such a big deal for today's games, and much more."

"Just wanted to say thanks for saving me time and also helping me out. (I learned a lot from it, too!) Keep up the most excellent work."

#### -Matt Burris, 3DGPU.com

"...this isn't so much a Knowledge base but a labor of love. Not only has this guide had a place in both Titch's and My Favorites for many years, but I'm really excited to see it still going after many, many years. Well done, Adrian. Keep up the excellent work."

#### -JohnL, The ModFathers.com

"Adrian Wong of Adrian's Rojak Pot has been building up his BIOS guide since late 1999. Today, he hit version 6.0, and the guide is now comprehensive in its scope. It comes highly recommended from me due to the fact that BIOS optimizations can yield positive results in performance and compatibility for everyone. Adrian also goes into far greater detail than even your best motherboard manual and even debunks some "myths" that some manufacturers still propagate."

#### -Ryu Connor, Tech-Report.com

"This is one of the most comprehensive and user-friendly guides I have found to date. I was able to do various tweaks with my mem/cpu that increased my overall system performance by about 15%.

Many of the BIOS tweaks will depend on your mobo and whether certain options are even available in your BIOS menu. However, I do recommend that even ppl that aren't familiar with working with the BIOS give it a go with this guide... Really helps to answer all your questions."

#### -James, TimSoft.com

"Some bookmarks occupy space in my Favorites folder just in case I need such a resource in the future, but others are frequent visits. I can easily see this one being a resource to which I refer often. This site contains very good explanations of the numerous configuration options you see in the BIOS.

...this truly is a link you'll want to keep around. This one is already sync'ed to my iPaq!"

#### -LockerGnome.com

"This is the most comprehensive BIOS Guide available. Just about every option in a modern BIOS is explained. The best performance setting is usually pointed out, and the explanations are easy to follow. A must for any overclocker wanna-be."

#### -Tim B., OCWorkbench.com

"I'd like to congratulate the author of the BIOS Optimization Guide. This is absolutely marvelous. I was looking specifically for advanced information on the AGP Aperture Size setting, and you guys have got TEN paragraphs on it."

-Sherman, Microsoft Support Services

# Breaking Through the BIOS Barrier

# Breaking Through the BIOS Barrier

# The Definitive BIOS Optimization Guide for PCs

Adrian Wong

An Imprint of PEARSON EDUCATION Upper Saddle River, NJ • New York • San Francisco • Toronto London • Munich • Paris • Madrid Capetown • Sydney • Tokyo • Singapore • Mexico City www.phptr.com

#### Library of Congress Cataloging-in-Publication Data

A CIP catalog record for this book can be obtained from the Library of Congress

Managing Editor: Gina Kanouse Production Supervision: Lori Lyons Composition: Tolman Creek Designs Cover Design Director: Jerry Votta Cover Design: Anthony Gemmellaro Manufacturing Manager: Dan Uhrig Acquisitions Editor: Bernard Goodwin Editorial Assistant: Michelle Vincenti Marketing Manager: Robin O'Brien Copy Editor: Sarah Cisco

2005 Pearson Education, Inc. Publishing as Prentice Hall Professional Technical Reference Upper Saddle River, New Jersey 07458

Prentice Hall PTR offers excellent discounts on this book when ordered in quantity for bulk purchases or special sales. For more information, please contact: U.S. Corporate and Government Sales, 1-800-382-3419, corpsales@pearsontechgroup.com. For sales outside of the U.S., please contact: International Sales, 1-317-581-3793, international@pearsontechgroup.com.

Company and product names mentioned herein are the trademarks or registered trademarks of their respective owners.

AMD, the AMD logo, AMD Athlon, AMD Duron, and combinations thereof are trademarks of Advanced Micro Devices, Inc.

All rights reserved. No part of this book may be reproduced, in any form or by any means, without permission in writing from the publisher. Prentice Hall PTR, One Lake Street, Upper Saddle River, NJ 07458.

Printed in the United States of America First Printing: August 2004 ISBN 0-13-145536-2 LOC 2004106506 Pearson Education Ltd.

Pearson Education Australia Pty., Limited Pearson Education South Asia Pte. Ltd. Pearson Education Asia Ltd. Pearson Education Canada, Ltd. Pearson Education de Mexico, S.A. de C.V. Pearson Education—Japan Pearson Malaysia S.D.N. B.H.D.

# Contents

| Foreword by Lewis Keller, Mushkin                                                                                                                                                                                                                                                                                                                                                                                                   | xxi                                                      |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|

| Introduction                                                                                                                                                                                                                                                                                                                                                                                                                        | 1                                                        |

| Chapter 1 What Is The Bios                                                                                                                                                                                                                                                                                                                                                                                                          | 5                                                        |

| How Does The BIOS Work?                                                                                                                                                                                                                                                                                                                                                                                                             | 5                                                        |

| The Motherboard BIOS                                                                                                                                                                                                                                                                                                                                                                                                                | 6                                                        |

| The BIOS Chip                                                                                                                                                                                                                                                                                                                                                                                                                       | 6                                                        |

| What Does It Do?                                                                                                                                                                                                                                                                                                                                                                                                                    | 7                                                        |

| Why Optimize the BIOS?                                                                                                                                                                                                                                                                                                                                                                                                              | 7                                                        |

| How Do I Optimize the BIOS?                                                                                                                                                                                                                                                                                                                                                                                                         | 8                                                        |

| BIOS Updates<br>How Do I Update the BIOS?<br>Determining the BIOSVersion<br>Obtaining the BIOS Update<br>Preparing a BIOS Hash Disk<br>Flashing the Motherboard BIOS                                                                                                                                                                                                                                                                | 8<br>9<br>9<br>10<br>12<br>12                            |

| Accessing the BIOS Setup Utility                                                                                                                                                                                                                                                                                                                                                                                                    | 14                                                       |

| The BIOS Setup Utility                                                                                                                                                                                                                                                                                                                                                                                                              | 14                                                       |

| Optimizing the BIOS                                                                                                                                                                                                                                                                                                                                                                                                                 | 14                                                       |

| Chapter 2 Special Topics                                                                                                                                                                                                                                                                                                                                                                                                            | 17                                                       |

| BIOS Emergencies                                                                                                                                                                                                                                                                                                                                                                                                                    | 17                                                       |

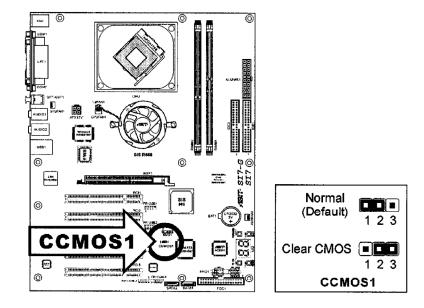

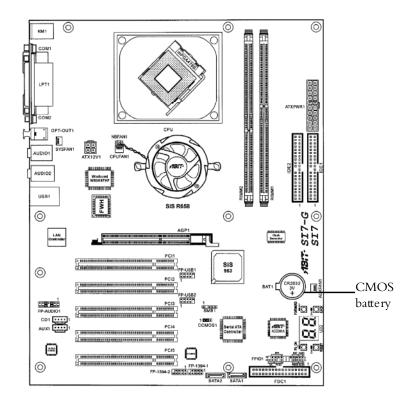

| Unbootable System<br>Power Off-Power On<br>Keyboard Reset<br>CMOS Discharge Jumper<br>CMOS Battery Removal                                                                                                                                                                                                                                                                                                                          | 17<br>17<br>18<br>18<br>19                               |

| Corrupted BIOS                                                                                                                                                                                                                                                                                                                                                                                                                      | 20                                                       |

| Hot Flashing<br>What Do I Need To Hot Flash a BIOS Chip?<br>Step 1 : Create a DOS Boot Disk<br>Step 2 : Prepare a Hot-Flash Capable Computer<br>Step 3 : Booting Up with the Boot Disk<br>Step 4 : Swap the BIOS Chips<br>Step 5 : Flash the Corrupted BIOS Chip<br>Step 6 : Swap the BIOS Chips Again<br>What If You Don't Have a Similar Motherboard?<br>Flashing With a Different Motherboard<br>The Universal BIOS Hash Utility | 21<br>22<br>23<br>24<br>24<br>24<br>25<br>26<br>26<br>27 |

| Summary                                                                                                                                                                                                                                                                                                                                                                                                                             | 27                                                       |

| Chapter 3 Quick Reviews 29 |                                             | 29       |

|----------------------------|---------------------------------------------|----------|

| Int                        | roduction                                   | 29       |

| #                          |                                             | 30       |

| ,,                         | 8-bit I/O Recovery Time                     | 30       |

|                            | 16-bit I/O Recovery Time                    | 30       |

|                            | 32-bit Disk Access                          | 30       |

|                            | 32-bit Transfer Mode                        | 30       |

| А                          |                                             | 32       |

| Α                          | Act Bank A to B CMD Delay                   | 32<br>32 |

|                            | AGP 2X Mode                                 | 32<br>32 |

|                            |                                             | 32<br>32 |

|                            | AGP 4X Drive Strength                       | 32<br>33 |

|                            | AGP 4X Mode<br>AGP 8X Mode                  | 33       |

|                            |                                             | 33       |

|                            | AGP Always Compensate<br>AGP Aperture Size  | 33<br>34 |

|                            |                                             | 34<br>34 |

|                            | AGP Capability<br>AGP Clock / CPU FSB Clock | 34<br>35 |

|                            | AGP Drive Strength                          | 35<br>35 |

|                            | AGP Drive Strength N Ctrl                   | 36       |

|                            | AGP Drive Strength P Ctrl                   | 36       |

|                            | AGP Driving Control                         | 36       |

|                            | AGP Driving Value                           | 30<br>37 |

|                            | AGP Fast Write                              | 35       |

|                            | AGP ISA Aliasing                            | 33<br>37 |

|                            | AGP Master 1WS Read                         | 38       |

|                            | AGP Master 1WS Write                        | 38       |

|                            | AGP Prefetch                                | 38       |

|                            | AGP Secondary Lat Timer                     | 39       |

|                            | AGP Spread Spectrum                         | 39       |

|                            | AGP to DRAM Prefetch                        | 40       |

|                            | AGPCLK / CPUCLK                             | 40       |

|                            | Anti-Virus Protection                       | 40       |

|                            | APIC Function                               | 41       |

|                            | Assign IRQ For USB                          | 41       |

|                            | Assign IRQ For VGA                          | 41       |

|                            | AT Bus Clock                                | 41       |

|                            | ATA100RAID IDE Controller                   | 42       |

|                            | Athlon 4 SSED Instruction                   | 42       |

|                            | Auto Detect DIMM/PCI Clk                    | 43       |

|                            | Auto Turn Off PCI Clock Pin                 | 43       |

| В                          |                                             | 44       |

| D                          | Boot Other Device                           | 44       |

|                            | Boot Sequence                               | 44       |

|                            | Boot Sequence EXT Means                     | 45       |

|                            | Boot To OS/2                                | 45       |

|                            | Boot Up Floppy Seek                         | 45       |

|                            | Boot Up NumLock Status                      | 45       |

|                            | Byte Merge                                  | 46       |

|                            |                                             |          |

Contents ix

| С |                               | 47 |

|---|-------------------------------|----|

|   | Clock Throttle                | 47 |

|   | Compatible FPU OP CODE        | 47 |

|   | CPU/DR AM CLK Synch CTL       | 48 |

|   | CPU Drive Strength            | 48 |

|   | CPU Fast String               | 48 |

|   | CPU Hyper-Threading           | 49 |

|   | CPU L2 Cache ECC Checking     | 49 |

|   | CPU Latency Timer             | 50 |

|   | CPU Level 1 Cache             | 50 |

|   | CPU Level 2 Cache             | 50 |

|   | CPU Level 3 Cache             | 51 |

|   | CPU Thermal-Throttling        | 51 |

|   | CPU to PCI Post Write         | 51 |

|   | CPU to PCIWrite Buffer        | 52 |

|   | CPU VCore Voltage             | 52 |

| D | C                             | 53 |

| D | DBI Output for AGP Trans.     | 53 |

|   | Delay DRAM Read Latch         | 53 |

|   | Delay IDE Initial             | 54 |

|   | Delay Prior To Thermal        | 54 |

|   | Delayed Transaction           | 55 |

|   | Differential Current          | 56 |

|   | Disable Unused PCI Clock      | 56 |

|   | DOS Flat Mode                 | 57 |

|   | DRAM Act to PreChrg CMD       | 57 |

|   | DRAM Burst Length 8QW         | 57 |

|   | DRAM Data Integrity Mode      | 58 |

|   | DRAM Idle Timer               | 58 |

|   | DRAM Interleave Time          | 59 |

|   | DRAM Page-Mode                | 59 |

|   | DRAM PreChrg to Act CMD       | 60 |

|   | DRAM Ratio (CPU:DRAM)         | 60 |

|   | DRAM Ratio H/W Strap          | 61 |

|   | DRAM Read Latch Delay         | 61 |

|   | DRAM Refresh Rate             | 62 |

|   | Duplex Select                 | 62 |

| Е | 1                             | 63 |

| Е | ECP Mode Use DMA              | 63 |

|   | EPP Mode Select               | 63 |

| _ | EFF Mode Select               |    |

| F |                               | 64 |

|   | Fast R-W Turn Around          | 64 |

|   | Fast Write to Read Turnaround | 64 |

|   | First Boot Device             | 64 |

|   | Flash BIOS Protection         | 65 |

|   | Floppy 3 Mode Support         | 65 |

|   | Floppy Disk Access Control    | 66 |

|   | Force 4-Way Interleave        | 66 |

#### x Contents

|   | Force Update ESCD             | 66 |

|---|-------------------------------|----|

|   | FPU OPCODE Compatible Mode    | 67 |

|   | Frame Buffer Size             | 67 |

|   | FSB Spread Spectrum           | 68 |

|   | Full Screen Logo              | 68 |

| G |                               | 69 |

|   | Gate A20 Option               | 69 |

|   | Graphic Win Size              | 69 |

|   | Graphic Window WR Combin      | 70 |

|   | Graphics Aperture Size        | 70 |

| Н |                               | 72 |

|   | Hardware Reset Protect        | 72 |

|   | HDD S.M.A.R.T. Capability     | 72 |

|   | Host Bus In-Order Queue Depth | 73 |

|   | Hyper-Threading Technology    | 73 |

| Ι |                               | 75 |

|   | IDE Bus Master Support        | 75 |

|   | IDE HDD Block Mode            | 75 |

|   | Init Display First            | 76 |

|   | In-Order Queue Depth          | 76 |

|   | Interrupt Mode                | 77 |

|   | IOQD                          | 77 |

|   | ISA 14.318MHz Clock           | 78 |

|   | ISA Enable Bit                | 78 |

| Κ |                               | 79 |

|   | K7 CLK_CTL Select             | 79 |

|   | KBC Input Clock Select        | 80 |

|   | Keyboard Auto-Repeat Delay    | 80 |

|   | Keyboard Auto-Repeat Rate     | 80 |

| L |                               | 81 |

|   | L3 Cache                      | 81 |

|   | LD-Off Dram RD/WR Cycles      | 81 |

|   | Level 2 Cache Latency         | 81 |

| Μ |                               | 83 |

|   | Master Drive PIO Mode         | 83 |

|   | Master Drive UltraDMA         | 83 |

|   | Master Priority Rotation      | 84 |

|   | MD Driving Strength           | 84 |

|   | Memory Hole At 15M-16M        | 85 |

|   | MP Capable Bit Identify       | 85 |

|   | MPS Control Version For OS    | 86 |

|   | MPS Revision                  | 86 |

|   | Multi-Sector Transfers        | 87 |

| Ν |                               | 88 |

|   | N/B Strap CPU As              | 88 |

|   | No Mask of SBA FE             | 88 |

| 0 |                               | 90 |

|   | Onboard FDC Swap A & B        | 90 |

|   | Onboard FDD Controller        | 90 |

**Contents** xi

|   | Onboard IDE-1 Controller    | 91  |

|---|-----------------------------|-----|

|   | Onboard IDE-2 Controller    | 91  |

|   | Onboard IR Function         | 92  |

|   | Onboard Parallel Port       | 92  |

|   | Onboard Serial Port 1       | 92  |

|   | Onboard Serial Port 2       | 93  |

|   | Onboard USB Controller      | 93  |

|   | OnChip VGA Mode Select      | 93  |

|   | OS/2 Onboard Memory > 64M   | 94  |

|   | OS Select For DRAM $> 64MB$ | 94  |

| Р |                             | 95  |

|   | P2C/C2P Concurrency         | 95  |

|   | Parallel Port Mode          | 95  |

|   | Passive R elease            | 96  |

|   | PCI#2 Access #1 Retry       | 96  |

|   | PCI 2.1 Compliance          | 97  |

|   | PCI Chaining                | 97  |

|   | PCI Clock / CPU FSB Clock   | 98  |

|   | PCI Delay Transaction       | 98  |

|   | PCI Dynamic Bursting        | 99  |

|   | PCI IDE Busmaster           | 100 |

|   | PCI IRQ Activated By        | 100 |

|   | PCI Latency Timer           | 100 |

|   | PCI Master 0 WS Read        | 101 |

|   | PCI Master 0 WS Write       | 101 |

|   | PCI Master Read Caching     | 102 |

|   | PCI Pipelining              | 102 |

|   | PCI Prefetch                | 102 |

|   | PCI Target Latency          | 103 |

|   | PCI to DRAM Prefetch        | 103 |

|   | PCI/VGA Palette Snoop       | 103 |

|   | PIO Mode                    | 104 |

|   | PIRQ x Use IRQ No.          | 104 |

|   | PNP OS Installed            | 105 |

|   | Post Write Combine          | 106 |

|   | Power On Function           | 107 |

|   | Primary Graphics Adapter    | 107 |

|   | Primary VGA BIOS            | 108 |

|   | Processor Number Feature    | 108 |

|   | PS/2 Mouse Function Control | 108 |

| Q |                             | 110 |

|   | Quick Boot                  | 110 |

|   | Quick Power On Self Test    | 110 |

| R |                             | 111 |

|   | Rank Interleave             | 111 |

|   | Read-Around-Write           | 111 |

|   | Read Wait State             | 111 |

|   | Refresh Interval            | 112 |

|   | Refresh Mode Select         | 112 |

|   | Report No FDD For Win95     | 112 |

|   | Reset Configuration Data    | 113 |

|   |                             |     |

|   | Resource Controlled By                               | 113 |

|---|------------------------------------------------------|-----|

|   | RxD, TxD Active                                      | 114 |

| S |                                                      | 115 |

|   | S2K Bus Driving Strength                             | 115 |

|   | S2K Strobe N Control                                 | 115 |

|   | S2K Strobe P Control                                 | 116 |

|   | SDRAM 1T Command                                     | 116 |

|   | SDRAM 1T Command Control                             | 117 |

|   | SDRAM Active to Precharge Delay                      | 117 |

|   | SDRAM Bank Interleave                                | 117 |

|   | SDRAM Bank-to-Bank Delay                             | 117 |

|   | SDRAM Bark Len                                       | 118 |

|   | SDRAM Burst Length                                   | 119 |

|   | SDRAM CAS Latency Time                               | 119 |

|   | SDRAM CAS Latency Time<br>SDRAM Command Leadoff Time | 119 |

|   | SDRAM Command Rate                                   | 120 |

|   |                                                      | 120 |

|   | SDRAM Cycle Length                                   | 120 |

|   | SDRAM Cycle Time Tras/Trc                            | 121 |

|   | SDRAM ECC Setting                                    |     |

|   | SDRAM Idle Limit                                     | 122 |

|   | SDRAM Leadoff Command                                | 122 |

|   | SDRAM Page Closing Policy                            | 123 |

|   | SDRAM Page Hit Limit                                 | 123 |

|   | SDRAM PH Limit                                       | 124 |

|   | SDRAM Precharge Control                              | 124 |

|   | SDRAM RAS Precharge Delay                            | 124 |

|   | SDRAM RAS Precharge Time                             | 125 |

|   | SDRAM RAS Pulse Width                                | 125 |

|   | SDRAM RAS-to-CAS Delay                               | 126 |

|   | SDRAM Row Active Time                                | 126 |

|   | SDRAM Row Cycle Time                                 | 126 |

|   | SDRAM Tras Timing Value                              | 127 |

|   | SDRAM Trc Timing Value                               | 127 |

|   | SDRAM Trcd Timing Value                              | 128 |

|   | SDRAM Trp Timing Value                               | 128 |

|   | SDRAM Bank-to-Bank Delay                             | 128 |

|   | SDRAM Trrd Timing Value                              | 129 |

|   | SDRAM Write Recovery Time                            | 129 |

|   | SDRAM Write to Read Command Delay                    | 129 |

|   | Second Boot Device                                   | 130 |

|   | Security Setup                                       | 130 |

|   | Shadowing Address Ranges                             | 130 |

|   | Share Memory Size                                    | 131 |

|   | Slave Drive PIO Mode                                 | 131 |

|   | Slave Drive UltraDMA                                 | 132 |

|   | Speed Error Hold                                     | 132 |

|   | Split Lock Operations                                | 133 |

|   | Spread Spectrum                                      | 133 |

|   | Super Bypass Mode                                    | 134 |

|   | Super Bypass Wait State                              | 134 |

|   | SuperStability Mode                                  | 134 |

|   | Swap Floppy Drive                                    | 135 |

|   |                                                      |     |

Contents

|            | Synchronous Mode Select                         | 136        |

|------------|-------------------------------------------------|------------|

|            | System BIOS Cacheable                           | 136        |

| Т          |                                                 | 137        |

| 1          | Third Boot Device                               | 137        |

|            | TX, RX Inverting Enable                         | 137        |

|            | Typematic Rate                                  | 137        |

|            | Typematic Rate Delay                            | 138        |

|            | Typematic Rate Setting                          | 138        |

| U          | <u>)</u> 1                                      | 139        |

| 0          | Ultra DMA Mode                                  | 139        |

|            | UltraDMA-100 IDE Controller                     | 139        |

|            | UltraDMA-133 IDE Controller                     | 140        |

|            | UltraDMA-66 IDE Controller                      | 140        |

|            | USB Controller                                  | 140        |

|            | USB Keyboard Support                            | 141        |

|            | USB Mouse Support                               | 141        |

|            | USWC Write Posting                              | 142        |

| <b>T</b> 7 | Cow C write rosung                              |            |

| V          |                                                 | 143        |

|            | Video BIOS Cacheable                            | 143        |

|            | Video BIOS Shadowing                            | 143        |

|            | Video Memory Cache Mode                         | 144        |

|            | Video RAM Cacheable                             | 145<br>145 |

|            | Virus Warning<br>VLink 8X Support               | 145        |

|            | 11                                              |            |

| W          |                                                 | 147        |

|            | Watchdog Timer                                  | 147        |

|            | Write Data In to Read Delay                     | 147        |

|            | Write Recovery Time                             | 148        |

| Chap       | ter 4 Detailed Descriptions                     | 149        |

| Int        | roduction                                       | 149        |

| #          |                                                 | 150        |

| ++         | 8-bit I/O Recovery Time                         | 150        |

|            | 16-bit I/O Recovery Time                        | 150        |

|            | 32-bit Disk Access                              | 150        |

|            | 32-bit Transfer Mode                            | 151        |

| •          | 32-bit fransier widde                           |            |

| А          |                                                 | 153        |

|            | Act Bank A to B CMD Delay                       | 153        |

|            | AGP 2X Mode                                     | 153        |

|            | AGP 4X Drive Strength<br>AGP 4X Mode            | 154<br>155 |

|            |                                                 |            |

|            | AGP 8X Mode                                     | 156        |

|            | AGP Always Compensate                           | 157<br>157 |

|            | AGP Aperture Size                               | 157        |

|            | AGP Capability<br>AGP Clock / CPU FSB Clock     | 159        |

|            | AGP Clock / CPO FSB Clock<br>AGP Drive Strength | 159        |

|            | AGP Drive Strength N Ctrl                       | 160        |

|            | AGP Drive Strength P Ctrl                       | 161        |

|            | AGP Driving Control                             | 162        |

|            |                                                 | 102        |

xii i

#### Contents

| AGP DrivingValue             | 163 |

|------------------------------|-----|

| AGP Fast Write               | 164 |

| AGP ISA Aliasing             | 164 |

| AGP Master 1WS Read          | 165 |

| AGP Master 1WS Write         | 166 |

| AGP Prefetch                 | 166 |

| AGP Secondary Lat Timer      | 167 |

| AGP Spread Spectrum          | 168 |

| AGP to DRAM Prefetch         | 169 |

| AGPCLK / CPUCLK              | 169 |

| Anti-Virus Protection        | 170 |

| APIC Function                | 170 |

| Assign IRQ For USB           | 171 |

| Assign IRQ ForVGA            | 171 |

| AT Bus Clock                 | 172 |

| ATA100RAID IDE Controller    | 173 |

| Athlon 4 SSED Instruction    | 174 |

| Auto Detect DIMM/PCI Clk     | 175 |

| Auto Turn Off PCI Clock Pin  | 175 |

| В                            | 176 |

| Boot Other Device            | 176 |

| Boot Sequence                | 176 |

| Boot Sequence EXT Means      | 177 |

| Boot To OS/2                 | 177 |

| Boot Up Floppy Seek          | 178 |

| Boot Up NumLock Status       | 178 |

| Byte Merge                   | 178 |

| С                            | 180 |

| Clock Throttle               | 180 |

| Compatible FPU OP CODE       | 181 |

| CPU Drive Strength           | 181 |

| CPU Fast String              | 182 |

| CPU Hyper-Threading          | 182 |

| CPU L2 Cache ECC Checking    | 184 |

| CPU Level 1 Cache            | 184 |

| CPU Level 2 Cache            | 185 |

| CPU Level 3 Cache            | 186 |

| CPU Thermal-Throttling       | 187 |

| CPU to PCI Post Write        | 188 |

| CPU to PCIWrite Buffer       | 189 |

| CPU VCore Voltage            | 189 |

| D                            | 191 |

| DBI Output for AGP Trans.    | 191 |

| Delay DRAM Read Latch        | 191 |

| Delay IDE Initial            | 191 |

| Delay Prior To Thermal       | 192 |

| Delayed Transaction          | 193 |

| Disable Unused PCI Clock     | 194 |

| DRAM Act to PreChrg CMD      | 195 |

| DRAM Burst Length 8QW        | 195 |

| DRAM Data Integrity Mode     | 190 |

| Division Data integrity with | 177 |

xiv

Contents \_\_\_\_\_ xv

|   | DRAM Idle Timer               | 198 |

|---|-------------------------------|-----|

|   | DRAM Interleave Time          | 200 |

|   | DRAM PreChrg to Act CMD       | 200 |

|   | DRAM Ratio (CPU:DRAM)         | 201 |

|   | DRAM Ratio H/W Strap          | 202 |

|   | DRAM Read Latch Delay         | 202 |

|   | DRAM Refresh Rate             | 203 |

|   | Duplex Select                 | 204 |

| Е |                               | 205 |

|   | ECP Mode Use DMA              | 205 |

|   | EPP Mode Select               | 205 |

| F |                               | 207 |

| • | Fast R-W Turn Around          | 207 |

|   | Fast Write to Read Turnaround | 207 |

|   | First Boot Device             | 208 |

|   | Flash BIOS Protection         | 208 |

|   | Floppy 3 Mode Support         | 209 |

|   | Floppy Disk Access Control    | 209 |

|   | Force 4-Way Interleave        | 210 |

|   | Force Update ESCD             | 210 |

|   | FPU OPCODE Compatible Mode    | 211 |

|   | FSB Spread Spectrum           | 212 |

|   | Full Screen Logo              | 212 |

| G |                               | 213 |

|   | Gate A20 Option               | 213 |

|   | Graphic Win Size              | 213 |

|   | Graphic Window WR Combin      | 214 |

|   | Graphics Aperture Size        | 214 |

| Н |                               | 216 |

|   | Hardware Reset Protect        | 216 |

|   | HDD S.M.A.R.T. Capability     | 216 |

|   | Host Bus In-Order Queue Depth | 217 |

|   | Hyper-Threading Technology    | 218 |

| Ι |                               | 220 |

|   | IDE Bus Master Support        | 220 |

|   | IDE HDD Block Mode            | 220 |

|   | Init Display First            | 221 |

|   | In-Order Queue Depth          | 222 |

|   | Interrupt Mode                | 223 |

|   | IOQD                          | 224 |

|   | ISA 14.318MHz Clock           | 225 |

|   | ISA Enable Bit                | 225 |

| Κ |                               | 228 |

|   | K7 CLK_CTL Select             | 228 |

|   | KBC Input Clock Select        | 229 |

|   | Keyboard Auto-Repeat Delay    | 230 |

|   | Keyboard Auto-Repeat Rate     | 230 |

| L |                               | 231 |

|   | L3 Cache                      | 231 |

|   | Level 2 Cache Latency         | 232 |

|   |                               |     |

## i **Contents**

| Μ |                                                      | 233        |

|---|------------------------------------------------------|------------|

|   | Master Drive PIO Mode                                | 233        |

|   | Master Drive UltraDMA                                | 234        |

|   | Master Priority Rotation                             | 235        |

|   | MD Driving Strength                                  | 236        |

|   | Memory Hole At 15M-16M                               | 236        |

|   | MP Capable Bit Identify                              | 237        |

|   | MPS Control Version For OS                           | 239        |

|   | MPS Revision                                         | 239        |

|   | Multi-Sector Transfers                               | 240        |

| Ν |                                                      | 241        |

|   | N/B Strap CPU As                                     | 241        |

|   | No Mask of SBA FE                                    | 241        |

| 0 |                                                      | 243        |

| 0 | Onboard FDC Swap A & B                               | 243<br>243 |

|   | Onboard FDD Controller                               | 243        |

|   | Onboard IDE-1 Controller                             | 243        |

|   | Onboard IDE-2 Controller                             | 244<br>244 |

|   | Onboard IR Function                                  | 244        |

|   | Onboard Parallel Port                                | 245<br>245 |

|   | Onboard Serial Port 1                                | 245<br>246 |

|   | Onboard Serial Port 2                                | 240<br>246 |

|   | Onboard USB Controller                               | 240<br>246 |

|   | OS/2 Onboard Memory > 64M                            | 240        |

|   | OS = OBOULD WEINDRY > 04MP OS Select For DRAM > 64MB | 247        |

| _ | OS SEICETTOT DICHWI > OFIND                          |            |

| Р |                                                      | 249        |

|   | P2C/C2P Concurrency                                  | 249        |

|   | Parallel Port Mode                                   | 249        |

|   | Passive R elease                                     | 250        |

|   | PCI#2 Access #1 Retry                                | 251        |

|   | PCI 2.1 Compliance                                   | 251        |

|   | PCI Chaining                                         | 252        |

|   | PCI Clock / CPU FSB Clock                            | 253        |

|   | PCI Delay Transaction                                | 254        |

|   | PCI Dynamic Bursting                                 | 255        |

|   | PCI IDE Busmaster                                    | 256        |

|   | PCI IRQ Activated By                                 | 257        |

|   | PCI Latency Timer                                    | 257        |

|   | PCI Master 0 WS Read                                 | 258        |

|   | PCI Master 0 WS Write                                | 258        |

|   | PCI Master Read Caching                              | 259        |

|   | PCI Pipelining                                       | 259        |

|   | PCI Prefetch                                         | 260        |

|   | PCI Target Latency                                   | 260        |

|   | PCI to DRAM Prefetch                                 | 261        |

|   | PCI/VGA Palette Snoop                                | 261        |

|   | PIO Mode                                             | 262        |

|   | PIRQ x Use IRQ No.                                   | 262        |

|   | PNP OS Installed                                     | 264        |

|   | Post Write Combine                                   | 266        |

xvi

Contents xvii

|   | Power On Function               | 267     |

|---|---------------------------------|---------|

|   | Primary Graphics Adapter        | 267     |

|   | Primary VGA BIOS                | 268     |

|   | Processor Number Feature        | 269     |

|   | PS/2 Mouse Function Control     | 269     |

| Q |                                 | 270     |

| ~ | Quick Boot                      | 270     |

|   | Quick Power On Self Test        | 270     |

| R | <u></u>                         | 271     |

| ĸ | Rank Interleave                 | 271 271 |

|   |                                 |         |

|   | Read-Around-Write               | 271     |

|   | Read Wait State                 | 272     |

|   | Refresh Interval                | 272     |

|   | Refresh Mode Select             | 273     |

|   | Report No FDD For Win95         | 274     |

|   | Reset Configuration Data        | 275     |

|   | Resource Controlled By          | 275     |

|   | RxD, TxD Active                 | 276     |

| S |                                 | 277     |

|   | S2K Bus Driving Strength        | 277     |

|   | S2K Strobe N Control            | 277     |

|   | S2K Strobe P Control            | 278     |

|   | SDRAM 1T Command                | 278     |

|   | SDRAM 1T Command Control        | 279     |

|   | SDRAM Active to Precharge Delay | 280     |

|   | SDRAM Bank Interleave           | 281     |

|   | SDRAM Bank-to-Bank Delay        | 282     |

|   | SDRAM Burst Len                 | 283     |

|   | SDRAM Burst Length              | 284     |

|   | SDRAM CAS Latency Time          | 285     |

|   | SDRAM Command Leadoff Time      | 285     |

|   | SDRAM Command Rate              | 286     |

|   | SDRAM Cycle Length              | 287     |

|   | SDRAM Cycle Time Tras/Trc       | 288     |

|   | SDRAM ECC Setting               | 288     |

|   | SDRAM Idle Limit                | 289     |

|   | SDRAM Leadoff Command           | 291     |

|   | SDRAM Page Closing Policy       | 291     |

|   | SDRAM Page Hit Limit            | 292     |

|   | SDRAM PH Limit                  | 293     |

|   | SDRAM Precharge Control         | 293     |

|   | SDRAM RAS Precharge Delay       | 294     |

|   | SDRAM RAS Precharge Time        | 295     |

|   | SDRAM RAS Pulse Width           | 295     |

|   | SDRAM RAS-to-CAS Delay          | 296     |

|   | SDRAM Row Active Time           | 297     |

|   | SDRAM Row Cycle Time            | 297     |

|   | SDRAM Tras Timing Value         | 298     |

|   | SDRAM Trc Timing Value          | 298     |

|   | SDRAM Trcd Timing Value         | 299     |

|   |                                 |         |

# xviii Contents

| Abou            | t the Author<br>t Adrian's Rojak Pot<br>t the BIOS Optimization Guide | 3 47<br>3 49<br>3 51 |

|-----------------|-----------------------------------------------------------------------|----------------------|

| Ac ron<br>Index | nym List                                                              | 3 29<br>3 35         |

|                 | Write Recovery Time                                                   | 327                  |

|                 | Write Data In to Read Delay                                           | 326                  |

|                 | Watchdog Timer                                                        | 326                  |

| W               |                                                                       | 326                  |

|                 | VLink 8X Support                                                      | 325                  |

|                 | Virus Warning                                                         | 324                  |

|                 | Video RAM Cacheable                                                   | 323                  |

|                 | Video Memory Cache Mode                                               | 322                  |

|                 | Video BIOS Shadowing                                                  | 321                  |

|                 | Video BIOS Cacheable                                                  | 320                  |

| V               | Video PIOS Cochechlo                                                  | 320                  |

| V               |                                                                       |                      |

|                 | USWC Write Posting                                                    | 318                  |

|                 | USB Mouse Support                                                     | 318                  |

|                 | USB Keyboard Support                                                  | 317                  |

|                 | USB Controller                                                        | 317                  |

|                 | UltraDMA-66 IDE Controller                                            | 316                  |

|                 | UltraDMA-133 IDE Controller                                           | 315                  |

|                 | UltraDMA-100 IDE Controller                                           | 315                  |

|                 | Ultra DMA Mode                                                        | 314                  |

| U               |                                                                       | 314                  |

|                 | Typematic Rate Setting                                                | 313                  |

|                 | Typematic Rate Delay                                                  | 313                  |

|                 | Typematic Rate                                                        | 312                  |

|                 | TX, RX Inverting Enable                                               | 312                  |

|                 | Third Boot Device                                                     | 312                  |

| Т               |                                                                       | 312                  |

| Ŧ               | System DIOS Cacheable                                                 |                      |

|                 | System BIOS Cacheable                                                 | 311                  |

|                 | Synchronous Mode Select                                               | 310                  |

|                 | Swap Floppy Drive                                                     | 309<br>310           |

|                 | Super Bypass Wait State<br>SuperStability Mode                        | 308<br>309           |

|                 | Super Bypass Mode                                                     | 308<br>308           |

|                 | Spread Spectrum<br>Super Byrpass Mode                                 | 307<br>308           |

|                 | Split Lock Operations                                                 | 306<br>307           |

|                 | 1                                                                     | 306                  |

|                 | Speed Error Hold                                                      | 305<br>306           |

|                 | Slave Drive UltraDMA                                                  | 305                  |

|                 | Slave Drive PIO Mode                                                  | 303<br>304           |

|                 | Shadowing Address Ranges<br>Share Memory Size                         | 303<br>303           |

|                 | Security Setup                                                        | 302                  |

|                 | Second Boot Device                                                    |                      |

|                 | SDRAM Write to Read Command Delay                                     | 301<br>302           |

|                 | SDRAM Write Recovery Time                                             | 301                  |

|                 | SDRAM Trrd Timing Value                                               | 300                  |

|                 | SDRAM Trp Timing Value                                                | 300                  |

|                 |                                                                       |                      |

# Acknowledgments

Like every new author, I started this project with the idea that all I needed to do was write the guide on BIOS options. It would be a cakewalk—or so I thought. Unfortunately, writing a book is really a lot more complex than it seems.

As I worked with my editor on the book, I found myself adding more and more material. Unlike the online version of the BIOS Optimization Guide, this book covers everything about the BIOS. This book is the truly complete BIOS Optimization Guide.

Unfortunately, because of my busy schedule, the development of this book has taken almost a year longer than we planned for. A thousand apologies to everyone, including my exasperated editor!

Now, I would like to thank my parents (*as everyone should*!) and my girlfriend, Jenny, for believing in my abilities and supporting me all the way through. Although they never understood why anyone would want to optimize the BIOS, I couldn't have done all this without them!

I would also like to thank the individuals who made significant contributions to this exhausting project—my editor, Bernard Goodwin; Lance Leventhal and Jim Markham at Prentice Hall; and of course, my pal, Chan Jo Wee!

Bernard, if you did not persist and guide this new writer through the pitfalls of writing a book, it wouldn't have become a reality. Thank you!

A big thank you also goes to both Lance and Jim for commenting on my work. You really helped me raise the standard of this book. Thank you!

I would also like to thank my pal, Jo Wee, for helping me handle the mundane aspects of this project. He was invaluable in allowing me to concentrate on writing the book instead of getting bogged down in clerical work. You are a savior, Jo Wee!

Finally, I would like to thank my buddies and core members of Team ARP—Ken Ng and Chai Ser Loon for helping me with Adrian's Rojak Pot while I finished the book. This book is as much a tribute to Team ARP as it is to everyone else who contributed to the book. Thank you, guys!

# Foreword

Breaking Through the BIOS Barrier: The Definitive BIOS Optimization Guide for PCs is absolutely the best guide of its kind.

Recent advances in technology have turned the user-friendly BIOS of the past into an engineer's maze of jargon and techno-babble. Most descriptions of BIOS settings from motherboard manufacturer's manuals give little more than a list of the available settings options. A description of the settings and an indication of how to set timings are virtually nonexistent.

*Breaking Through the BIOS Barrier* solves all that by providing easy-to-understand, layman's descriptions for all of the latest BIOS settings.

Combining these descriptions with real-world reasons for choosing certain options makes the guide an invaluable resource to any computer "tweaker" or enthusiast. For the advanced user and the curious, the book is full of technical information that delves deeply into the mysterious and uncharted waters of the modern BIOS setup.

Memory timings are an extremely important part of performance and stability in today's highend computers. At Mushkin, Adrian Wong's online BIOS Optimization Guide

(http://www.rojakpot.com/bog.aspx) has helped us give accurate, bleeding-edge suggestions to our customers to increase performance and stability. It has been an indispensable tool for our technical personnel to use in R&D and troubleshooting.

Kudos to Adrian Wong!

#### Lewis Keller

Technical Services Manager, Mushkin Enhanced Memory Systems, Inc. http://www.mushkin.com/

# **Introduction** What Is the BIOS?

Welcome to the first edition of *Breaking Through the BIOS Barrier: The Definitive BIOS* Optimization Guide for PCs.

Most people never think about what actually goes on when using a computer. To many, a computer simply reacts to a series of keyboard entries and clicks. Whatever the computer is commanded to do, it just does. No questions asked.

In reality, it isn't as simple as that. Behind the facade of the user-friendly graphical user interface, many things have to be done by the system for a command to be carried out.

Enter the BIOS, which is short for **Basic Input/Output System**.

By definition, it is the interface between software and hardware that allows them both to communicate and interact with each other. While you may think that the BIOS only exists in the form of the motherboard BIOS, it is actually the combination of the motherboard BIOS, the BIOS of all add-on cards in the system, as well as their device drivers.

In the early days of personal computing, the BIOS was off-limits to the user. Access was restricted to only a few basic functions, just enough for the system assembler to get the computer running. Knowledge about the BIOS at that time was nothing short of arcane.

Yet today, the situation is not much better. Yes, motherboard manufacturers are allowing a lot more access to the various BIOS options. This gives us more flexibility in setting up and optimizing the computer. However, little has been done about educating the user about what each BIOS option actually does.

Take a look at the BIOS section of any motherboard manual. It would be very surprising if you manage to extract anything useful out of the terse, cryptic explanations. How is anyone expected to optimize the BIOS when no one knows what each BIOS option does?

I started writing this BIOS guide back in 1999 as a simple online guide on how to optimize the BIOS. Today, it not only covers BIOS optimization, it has also become a comprehensive guide on over 250 BIOS options.

This book not only teaches you how to optimize each BIOS option, you also learn what each BIOS option does and the reason behind each recommended setting. In the end, you will be able to optimize the BIOS like a professional!

#### 2 Introduction What Is the BIOS?

#### **Book Objectives**

Breaking Through the BIOS Barrier was written with several key objectives in mind.

It was primarily written to help the reader optimize the BIOS. Unfortunately, BIOS optimization isn't a clear-cut problem that can be solved by simply following some fixed guidelines.

Although many simple guidelines and recommendations are covered in this book, hardware and software configurations vary from computer to computer. Therefore, it is important that the reader understands what each BIOS option does so that he or she can make the best decision for the computer in question.

To that end, this book not only helps you optimize the BIOS with many guidelines and recommendations, it also helps you understand what each BIOS option does, so you can make the necessary adjustments for your system.

This book aims to dispel the misinformation about many BIOS options that have been propagated by both media and manufacturers alike. For too many years now, motherboard manuals and various computer books have been spreading inaccurate information and recommendations on many BIOS options. It's time to change that for good!

This book also discusses basic topics about the BIOS to provide a solid foundation on the BIOS and how to keep it updated as well as access its setup menu.

When you finish reading this book, you will have all the necessary knowledge you need to fully optimize the BIOS of your computer!

#### Who Is This Book For?

This book is for those (novice or advanced) who are interested in optimizing the BIOS for performance and stability.

You will learn what the BIOS is, the different types of BIOS, how to access your BIOS, and how to update it. You also will learn what each BIOS option does and what you should set for optimal performance and stability.

This book also teaches you about BIOS emergencies like an unbootable computer or a corrup ted BIOS. What should you do? How can you correct the problem? This book covers all that, including a look at the hot flash method.

For the novice, Chapters 1 and 2 are just what you need. If you are familiar with computers and want to understand what each BIOS option really does, turn to Chapters 3 and 4.

#### **Chapter Breakdown**

*Breaking Through the BIOS Barrier* is really two books in one. Chapters 1 and 2 provide a solid foundation of BIOS basics and special topics in a narrative fashion, while Chapters 3 and 4 are presented in a more structured manner for easy reference. Here, you not only learn everything about each BIOS option, you also learn the logic behind each optimization.

# **Chapter 1: BIOS Basics**

Chapter 1 serves as an introduction to the BIOS. It deals with basic topics on the BIOS. In this chapter, you learn what the BIOS really is, how it works, how to keep it updated, and how to access it.

# **Chapter 2: Special Topics**

Chapter 2 deals with special topics like BIOS emergencies and hot flashing. If you ever run into trouble with the BIOS, head straight for this chapter. It can help you restore your BIOS.

# **Chapter 3: Quick Reviews**

Chapter 3 offers a simplified explanation of each BIOS option as well as its recommended settings. Flip to this chapter if you need a quick overview of a BIOS option and its optimal settings. This is targeted at those with little hardware knowledge.

# **Chapter 4: Detailed Descriptions**

Chapter 4 deals with each BIOS option in much greater detail. If you already have a moderate level of hardware knowledge, this section allows you to achieve a greater understanding of the various BIOS options and the logic behind their recommended settings.

Please note that certain BIOS options may appear similar in both the Quick Reviews and Detailed Descriptions sections.

### **Acronym List**

Following Chapter 4, you will find a complete alphabetical list of acronyms used throughout the book. Refer to this list if you want to quickly see an acronym spelled out.

### **Category Lookup Table**

Printed on the inside front and back covers of this book is the Category Lookup Table. The BIOS features have been arranged according to different sub systems so that you can easily search for the BIOS feature of your choice. If the BIOS feature you are interested is not listed within the book (because it has a different name), you can try checking the Category Lookup Table for a similar BIOS feature.

# Chapter 1 What Is the BIOS?

The **BIOS** is short for **Basic Input/Output System**. By definition, it is the interface between software and hardware that allows software and hardware to communicate and interact with each other.

The BIOS is made up of everything that allows software and hardware to interact with each other. While you may think that the BIOS only exists in the form of the motherboard BIOS, it is actually the combination of the motherboard BIOS, the BIOS of all add-on cards in the system, as well as their device drivers.

### How Does the BIOS Work?

Most people never think about what actually goes on when they do something on the computer. To most people, whenever they command the computer to do something, it just does it. No questions asked.

It isn't as simple as that. Behind the facade of the user-friendly **GUI** (**Graphical User Interface**), many things have to be done by the system for the command to be carried out.

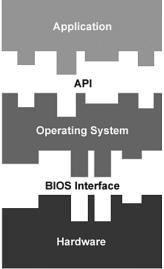

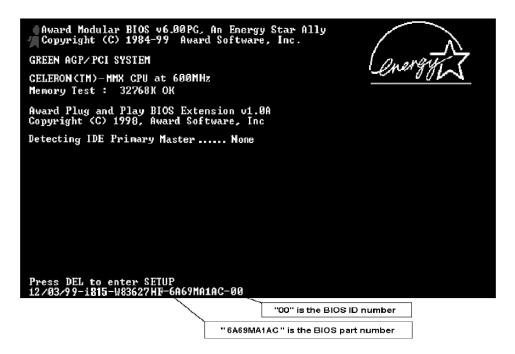

Let's visualize the computer system as three separate layers that communicate with each other through different interfaces. The diagram to the right is of that layered division:

In our layered system, the application is the highest level. It cannot directly interact with the hardware. It can only communicate with the operating system through the **API** or **Application Program Interface**.

The API is a set of common functions that the application calls upon to get the operating system to do what it wants. Because the API is operating system-specific, it differs from operating

system to operating system. However, irrespective of the operating system, the API allows the application to get the job done without knowing how the operating system does it. The application doesn't need to know anything about the computer's hardware.

The operating system then communicates to the BIOS what it needs to carry out the application's request. The operating system never communicates directly with the hardware.

The different layers and interfaces.

#### 6 Chapter 1 What Is the BIOS?

The BIOS layer allows the operating system to support all manners of hardware. Each piece of hardware comes with its own BIOS and/or driver, which become part of the system's BIOS.

Therefore, the BIOS layer is dynamic and changes to match the computer's hardware configuration. It serves to mask the differences between different hardware by presenting a common interface to the operating system.

The operating system only needs to know how to communicate with the BIOS layer. It is up to the BIOS layer to translate the operating system commands into action by the hardware.

Without the BIOS layer, there's no way the operating system can access the hardware layer. The BIOS layer is the operating system's key to the hardware layer. That's how important the BIOS layer is in the computer system.

# The Motherboard BIOS

Although, by definition, the BIOS consists of the motherboard BIOS, the BIOS of all add-on cards in the system, as well as their drivers, we will be concentrating on the motherboard BIOS in this book.

The motherboard BIOS is the most important component of the BIOS layer. This is because it contains all the software needed to get the computer started. It also comes with basic diagnostics and configuration utilities.

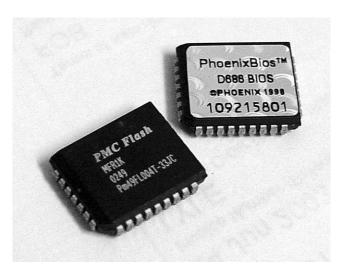

# The BIOS Chip

The motherboard BIOS is stored in a chip on the motherboard. The BIOS chip normally comes in the form of a rectangular **DIP** (**Dual In-line Package**) or a square **PLCC** (**Plastic Leaded Chip Carrier**) package.

The capacity of BIOS chips is measured in Megabits (Mb). Most BIOS chips these days are 2Mb (256KB) in size. These higher capacity chips allow the manufacturer to offer more features than is possible with the smaller 1Mb chips.

However, please note that the size of the BIOS chip has nothing to do with its performance. The choice of type and size of the BIOS chip is a matter of economics and requirements, rather than performance.

PLCC-type BIOS chips. (Photo by author.)

# What Does It Do?

Here is a breakdown of what the motherboard BIOS actually consists of:

- Power-on diagnostic tests

- System configuration utility

- Bootstrap loader

- BIOS interface

When you boot up the computer, it initiates the **POST (Power-On Diagnostic Test)**. The POST serves as a quick-and-dirty way to make sure that all the critical components are functioning.

After the POST sequence completes, you are given the opportunity to access the system configuration utility. This utility allows you to configure and modify a range of features. These BIOS features show you just how important the BIOS is.

These BIOS features control every aspect of the computer, from the speed at which the processor runs to the transfer mode of the hard disk. It goes without saying that these BIOS features are the reason why I'm writing this book. We go into details later in Chapter 4.

After the short delay, the BIOS starts the bootstrap loader routine, which scans for a valid master boot sector on all available drives. This can be anything from a hard disk to a CD-ROM drive. The master boot sector is just a predetermined area containing code that initiates the loading of the operating system.

When executed, the master boot sector turns over the booting process to the operating system by loading the operating system's boot sector. The operating system then starts loading up its core files.

In most cases, this is where the BIOS' role ends because current operating systems employ their own 32-bit or 64-bit drivers, which offer far superior functionality and performance to the BIOS' basic drivers. However, the BIOS' core drivers still have some importance.

Even modern operating systems like Microsoft Windows still need to use the BIOS' basic drivers, albeit only in their troubleshooting or "safe" modes. This is because the core BIOS drivers have been standardized a long time ago, and every piece of hardware made since then is backward-compatible with them.

While these core BIOS drivers may be slow and primitive, they are guaranteed to work with any hardware designed for the PC. That's why they are still an integral part of every PC.

## Why Optimize the BIOS?

Although the BIOS only functions from the time you press the Power On button until the operating system takes over, its effects last as long as the computer is operational. Whatever you set in the BIOS greatly determines your computing experience.

If the BIOS is not configured properly, you may be able to boot up the operating system and run it for a while. However, the system will become unstable and eventually crash. This will go on and on, ad nauseum.

#### 8 Chapter 1 What Is the BIOS?

You may send it back to your computer dealer and, more likely than not, the technician will simply reset the BIOS to its fail-safe settings and send it back to you. However, is that the best solution?

Most definitely not! An unoptimized BIOS means an unoptimized system. Not only will it take longer to boot up or initialize devices, it will also slow down the entire computer. It's like kneecapping someone before sending him out to do the long jump!

BIOS optimization is critical not only to the optimal performance of the computer, but also to the proper functioning of the system's components. Computers these days are made up of a hodge-podge of different components from different manufacturers. This presents a real problem when it comes to getting them all to work together.

Because of the variety of components that make up any one computer, it is impossible for manufacturers to optimize their motherboards for any particular configuration. That's why all motherboards come with configurable BIOS.

The BIOS allows the OEM (Original Equipment Manufacturer), as well as the end-user, to modify settings and timings to support different configurations. Without them, manufacturers would be forced to use the most conservative settings, which would greatly degrade performance.

# How Do I Optimize the BIOS?

The key to optimizing the BIOS lies in its built-in system configuration utility. As mentioned earlier, this is where you can configure or modify a variety of BIOS features and options.

These BIOS features show you just how important the BIOS is. They control every aspect of the computer, from the speed at which the processor runs to the transfer mode of the hard disk. This book teaches you how to optimize your BIOS for proper operation and maximum performance. Let's turn that snail into a road hog!

### **BIOS Updates**

First of all, you should know that the BIOS that ships with your motherboard is not necessarily the latest version or the most stable version. Reputable motherboard manufacturers constantly improve on their motherboard BIOS and regularly release BIOS updates.

These BIOS updates are important because they correct bugs and sometimes provide additional capabilities. You can think of them as driver updates or software patches. You should always keep the motherboard BIOS up to date.

In the following figure, you can see the list of changes in two BIOS updates for the ABIT NF7-S motherboard.

#### BIOS Updates 9

| 1171                                 | 9.exe Bios Issue Date:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 2003/05/1 |

|--------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|

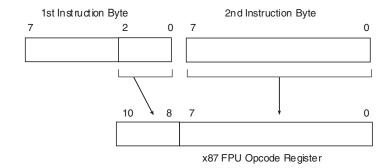

| 1.                                   | Please use AWDFLASH 8.23D or later to update NF7 series BIOS.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |           |