# EDITION SECOND EDITION ENGINEERING DIGITAL DESIGN

#### RICHARD F. TINDER

REVISED

# Engineering Digital Design

Second Edition, Revised

This page intentionally left blank

# Engineering Digital Design

Second Edition, Revised

#### by

**RICHARD F. TINDER** School of Electrical Engineering and Computer Science Washington State University Pullman, Washington

A Harcourt Science and Technology Company

SAN DIEGO/SAN FRANCISCO/NEW YORK/BOSTON/LONDON/SYDNEY/TOKYO

This book is printed on acid-free paper.  $\textcircled{\begin{tmatrix} \hline \end{tmatrix}}$

Copyright ©2000, Elsevier Science (USA).

All Rights Reserved.

No part of this publication may be reproduced or transmitted in any form or by any means, electronic or mechanical, including photocopy, recording, or any information storage and retrieval system, without **per**mission in writing from the publisher.

Requests for permission to make copies of any part of the work should be mailed to: Permissions Department, Academic Press, 6277 Sea Harbor Drive, Orlando, Florida 32887-6777

Academic Press An imprint of Elsevier Science 525 B Street, Suite 1900, San Diego, California 92101-4495, USA http://www.academicpress.com

Academic Press 84 Theobalds Road, London WC1X 8RR, UK http://www.academicpress.com

Library of Congress Catalog Card Number: 99-066780

International Standard Book Number: 0-12-691295-5

PRINTED IN THE UNITED STATES OF AMERICA

02

03

04

05

06

07

MV

9

8

7

6

5

4

3

2

#### Disclaimer:

This eBook does not include the ancillary media that was packaged with the original printed version of the book. This book is lovingly dedicated to my partner in life, Gloria

This page intentionally left blank

For the sake of persons of different types, scientific truth should be presented in different forms, and should be regarded as equally scientific, whether it appears in the robust form and the vivid coloring of a physical illustration, or in the tenuity and paleness of a symbolic expression.

> James Clerk Maxwell Address to the Mathematics and Physical Section, British Association of Sciences, 1870

This page intentionally left blank

# Contents

| Preface |       |                                                         | xix |

|---------|-------|---------------------------------------------------------|-----|

| 1.      | Intro | 1                                                       |     |

|         | 1.1   | What Is So Special about Digital Systems?               | 1   |

|         | 1.2   | The Year 2000 and Beyond?                               | 3   |

|         | 1.3   | A Word of Warning                                       | 5   |

|         | 1.4   | Glossary of Terms, Expressions, and Abbreviations       | 5   |

| 2.      | Num   | ber Systems, Binary Arithmetic, and Codes               | 31  |

|         | 2.1   | Introduction                                            | 31  |

|         | 2.2   | Positional and Polynomial Representations               | 32  |

|         | 2.3   | Unsigned Binary Number System                           | 33  |

|         | 2.4   | Unsigned Binary Coded Decimal, Hexadecimal, and Octal   | 34  |

|         |       | 2.4.1 The BCD Representation                            | 34  |

|         |       | 2.4.2 The Hexadecimal and Octal Systems                 | 36  |

|         | 2.5   | Conversion between Number Systems                       | 37  |

|         |       | 2.5.1 Conversion of Integers                            | 38  |

|         |       | 2.5.2 Conversion of Fractions                           | 40  |

|         | 2.6   | Signed Binary Numbers                                   | 43  |

|         |       | 2.6.1 Signed-Magnitude Representation                   | 44  |

|         |       | 2.6.2 Radix Complement Representation                   | 45  |

|         |       | 2.6.3 Diminished Radix Complement Representation        | 48  |

|         | 2.7   | Excess (Offset) Representations                         | 49  |

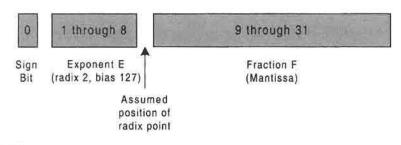

|         | 2.8   | Floating-Point Number Systems                           | 49  |

|         | 2.9   | Binary Arithmetic                                       | 52  |

|         |       | 2.9.1 Direct Addition and Subtraction of Binary Numbers | 52  |

|         |       | 2.9.2 Two's Complement Subtraction                      | 53  |

|         |       | 2.9.3 One's Complement Subtraction                      | 54  |

|         |       | 2.9.4 Binary Multiplication                             | 55  |

|         |       | 2.9.5 Binary Division                                   | 58  |

|         |       | 2.9.6 BCD Addition and Subtraction                      | 62  |

|         |       | 2.9.7 Floating-Point Arithmetic                         | 64  |

|         |       | 2.9.8 Perspective on Arithmetic Codes                   | 67  |

|         | 2.10  | Other Codes                                             | 68  |

|         |       | 2.10.1 The Decimal Codes                                | 68  |

|         |       | 2.10.2 Error Detection Codes                            | 69  |

|         |       | 2.10.3 Unit Distance Codes                              | 70  |

|         |       | 2.10.4 Character Codes                                  | 70  |

|         |       | Further Reading                                         | 72  |

|         |       | Problems                                                | 72  |

| 4.1Introduction1314.2SOP and POS Forms1314.2.1The SOP Representation1314.2.2The POS Representation1344.3Introduction to Logic Function Graphics1374.3.1First-Order K-maps1384.3.2Second-Order K-maps1384.3.3Third-Order K-maps140                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 3. | Back  | ground    | for Digital Design                                                 | 79  |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|-------|-----------|--------------------------------------------------------------------|-----|--|

| 3.2.1       Binary State Terminology and Symbology       79         3.3       Introduction to CMOS Terminology and Symbology       82         3.4       Logic Level Conversion: The Inverter       83         3.5       Transmission Gates and Tri-State Drivers       84         3.6       AND and OR Operators and Their Mixed-Logic Circuit Symbology       87         3.6.1       Logic Circuit Symbology for AND and OR       87         3.6.2       NAND Gate Realization of Logic AND and OR       88         3.6.3       NOR Gate Realization of Logic AND and OR       89         3.6.4       NAND and NOR Gate Realization of Logic Level Conversion       90         3.6.5       The AND and OR Gates and Their Realization of Logic       92         3.6.6       Summary of Logic Circuit Symbols for the AND and OR Functions and Logic Level Conversion       94         3.7       Logic Level Incompatibility: Complementation       95         3.8       Reading and Construction of Mixed-Logic Circuit Symbology       98         3.9.1       The XOR and EQV Functions of the XOR Gate       100         3.9.2       The XOR and EQV Functions of the XOR and EQV Gircuit Symbols       102         3.9.5       Summary of Conjugate Logic Circuit Symbols for XOR and EQV Gate       103         3.9.6       Construction and Wave                                                                             |    | 3.1   | Introdu   | action                                                             | 79  |  |

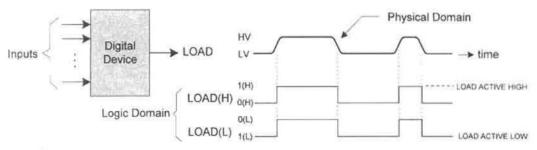

| 3.2.1       Binary State Terminology and Symbology       79         3.3       Introduction to CMOS Terminology and Symbology       82         3.4       Logic Level Conversion: The Inverter       83         3.5       Transmission Gates and Tri-State Drivers       84         3.6       AND and OR Operators and Their Mixed-Logic Circuit Symbology       87         3.6.1       Logic Circuit Symbology for AND and OR       87         3.6.2       NAND Gate Realization of Logic AND and OR       88         3.6.3       NOR Gate Realization of Logic AND and OR       89         3.6.4       NAND and NOR Gate Realization of Logic Level Conversion       90         3.6.5       The AND and OR Gates and Their Realization of Logic       92         3.6.6       Summary of Logic Circuit Symbols for the AND and OR Functions and Logic Level Conversion       94         3.7       Logic Level Incompatibility: Complementation       95         3.8       Reading and Construction of Mixed-Logic Circuit Symbology       98         3.9.1       The XOR and EQV Functions of the XOR Gate       100         3.9.2       The XOR and EQV Functions of the XOR and EQV Gircuit Symbols       102         3.9.5       Summary of Conjugate Logic Circuit Symbols for XOR and EQV Gate       103         3.9.6       Construction and Wave                                                                             |    | 3.2   |           |                                                                    | 79  |  |

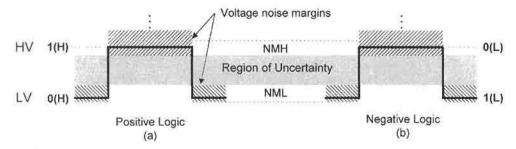

| 3.3       Introduction to CMOS Terminology and Symbology       82         3.4       Logic Level Conversion: The Inverter       83         3.5       Transmission Gates and Tri-State Drivers       84         3.6       AND and OR Operators and Their Mixed-Logic Circuit Symbology       87         3.6.1       Logic Circuit Symbology for AND and OR       88         3.6.2       NAND Gate Realization of Logic AND and OR       88         3.6.3       NOR Gate Realization of Logic AND and OR       89         3.6.4       NAND and NOR Gate Realization of Logic Lovel Conversion       90         3.6.5       The AND and OR Gates and Their Realization of Logic       92         3.6.6       Summary of Logic Circuit Symbols for the AND and OR Functions and Logic Level Conversion       94         3.7       Logic Level Incompatibility: Complementation       95         3.8       Reading and Construction of Mixed-Logic Circuit Symbology       98         3.9.1       The XOR and EQV Functions of the XOR Gate       100         3.9.2       The XOR and EQV Functions of the XOR and EQV Functions       101         3.9.3       Multiple Gate Realizations of the XOR and EQV Circuit Symbols       103         3.9.4       The Effect of Active Low Inputs to the XOR and EQV Circuit Symbols       103         3.9.5                                                                                    |    |       | -         |                                                                    | 79  |  |

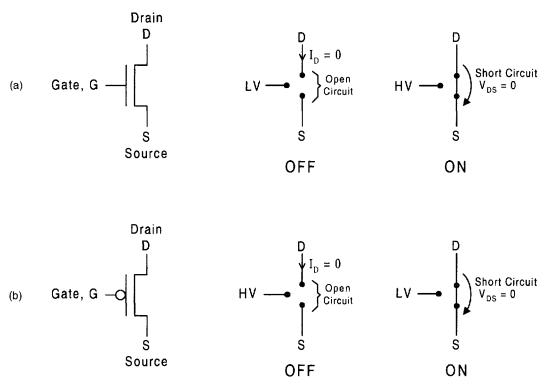

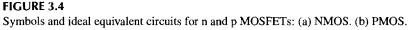

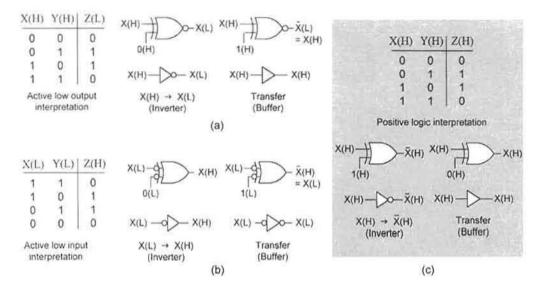

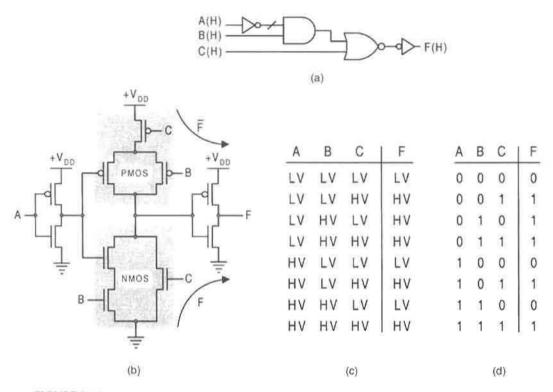

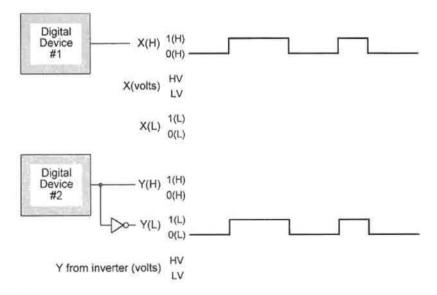

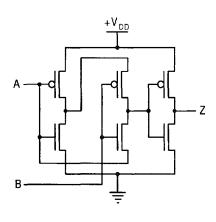

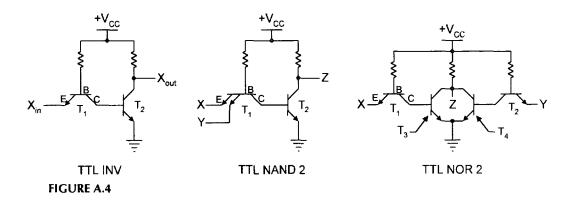

| 3.4       Logic Level Conversion: The Inverter       83         3.5       Transmission Gates and Tri-State Drivers       84         3.6       AND and OR Operators and Their Mixed-Logic Circuit Symbology       87         3.6.1       Logic Circuit Symbology for AND and OR       87         3.6.2       NAND Gate Realization of Logic AND and OR       88         3.6.3       NOR Gate Realization of Logic AND and OR       89         3.6.4       NAND and NOR Gate Realization of Logic Level Conversion       90         3.6.5       The AND and OR Gates and Their Realization of Logic       92         3.6.6       Summary of Logic Circuit Symbols for the AND and OR Functions and Logic Level Conversion       94         3.7       Logic Circuit Symbols for the AND and OR Functions       94         3.7       Logic Level Incompatibility: Complementation       95         3.8       Reading and Construction of Mixed-Logic Circuit Symbology       98         3.9.1       The XOR and EQV Functions of the XOR Gate       100         3.9.2       The XOR and EQV Functions of the XOR and EQV Circuit Symbols       101         3.9.4       The Effect of Active Low Inputs to the XOR and EQV Circuit Symbols       102         3.9.5       Summary of Conjugate Logic Circuit Symbols for XOR and EQV Gate       103         3.9.6 <td>3.3</td> <td>Introdu</td> <td></td> <td>82</td>                    |    | 3.3   | Introdu   |                                                                    | 82  |  |

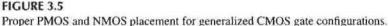

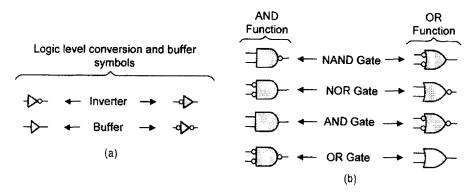

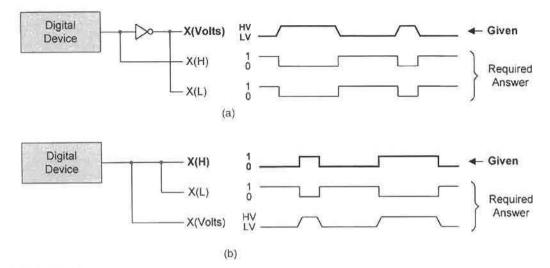

| 3.5       Transmission Gates and Tri-State Drivers       84         3.6       AND and OR Operators and Their Mixed-Logic Circuit Symbology       87         3.6.1       Logic Circuit Symbology for AND and OR       88         3.6.2       NAND Gate Realization of Logic AND and OR       88         3.6.3       NOR Gate Realization of Logic Level Conversion       90         3.6.4       NAND and NOR Gate Realization of Logic Level Conversion       90         3.6.5       The AND and OR Gates and Their Realization of Logic Level Conversion       90         3.6.6       Summary of Logic Circuit Symbols for the AND and OR Functions and Logic Level Conversion       94         3.7       Logic Level Incompatibility: Complementation       95         3.8       Reading and Construction of Mixed-Logic Circuit Symbology       98         3.9.1       The XOR and EQV Functions of the XOR Gate       100         3.9.2       The XOR and EQV Functions of the XOR and EQV Gates       101         3.9.4       The Effect of Active Low Inputs to the XOR and EQV Gates       103         3.9.5       Summary of Conjugate Logic Circuit Symbols for XOR and EQV Gates       103         3.9.6       Controlled Logic Level Conversion       103         3.9.7       Construction and Waveform Analysis of Logic Circuits Containing XOR -Type Functions       104 <td></td> <td>3.4</td> <td colspan="4"></td> |    | 3.4   |           |                                                                    |     |  |

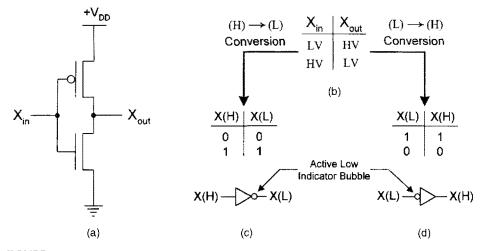

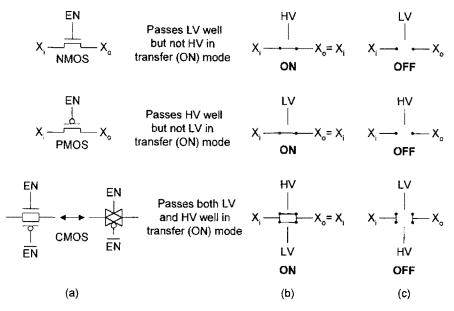

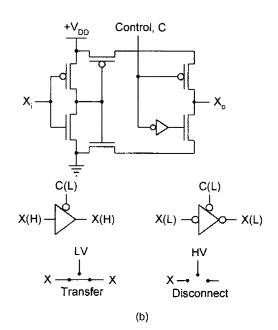

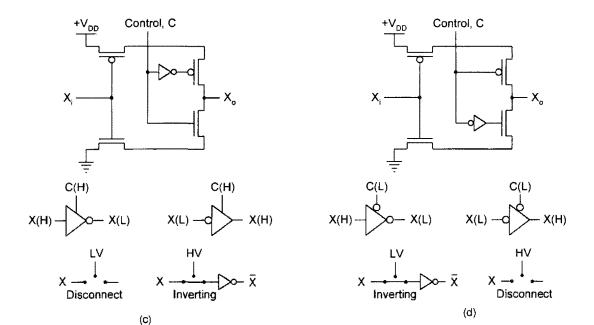

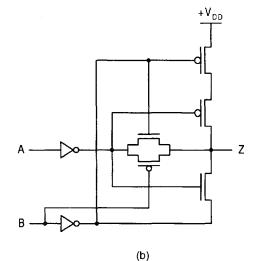

| 3.6       AND and OR Operators and Their Mixed-Logic Circuit Symbology       87         3.6.1       Logic Circuit Symbology for AND and OR       87         3.6.2       NAND Gate Realization of Logic AND and OR       88         3.6.3       NOR Gate Realization of Logic AND and OR       89         3.6.4       NAND and NOR Gate Realization of Logic Level Conversion       90         3.6.5       The AND and OR Gates and Their Realization of Logic       92         3.6.6       Summary of Logic Circuit Symbols for the AND and OR Functions and Logic Level Iconversion       94         3.7       Logic Circuit Symbology       98         3.8       Reading and Construction of Mixed-Logic Circuit Symbology       98         3.9       XOR and EQV Operators and Their Mixed-Logic Circuit Symbology       98         3.9.1       The XOR and EQV Functions of the XOR Gate       100         3.9.2       The XOR and EQV Functions of the XOR and EQV Circuit Symbols       102         3.9.4       The Effect of Active Low Inputs to the XOR and EQV Circuit Symbols       102         3.9.5       Summary of Conjugate Logic Circuit Symbols for XOR and EQV Gates       103         3.9.6       Controlled Logic Level Conversion       103         3.9.7       Construction and Waveform Analysis of Logic Circuit Symbols       104                                                                        |    | 3.5   |           |                                                                    | 84  |  |

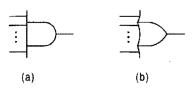

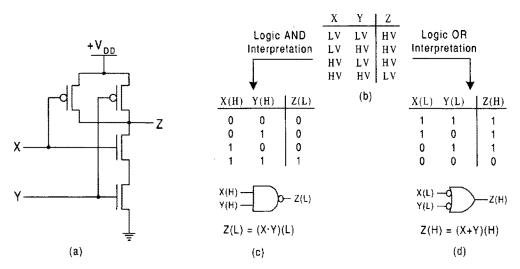

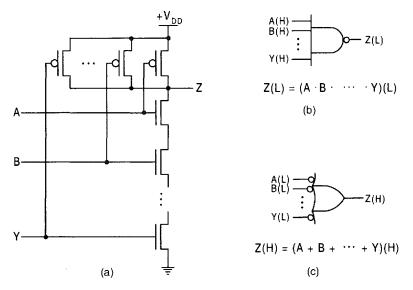

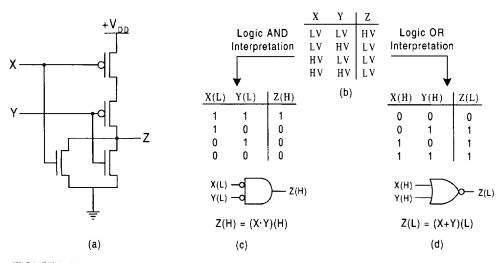

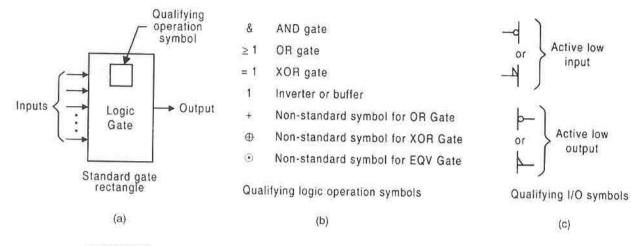

| 3.6.2       NAND Gate Realization of Logic AND and OR       88         3.6.3       NOR Gate Realization of Logic Level Conversion       90         3.6.4       NAND and NOR Gate Realization of Logic Level Conversion       90         3.6.5       The AND and OR Gates and Their Realization of Logic       92         3.6.6       Summary of Logic Circuit Symbols for the AND and OR Functions and Logic Level Conversion       94         3.7       Logic Level Incompatibility: Complementation       95         3.8       Reading and Construction of Mixed-Logic Circuits       97         3.9       XOR and EQV Operators and Their Mixed-Logic Circuit Symbology       98         3.9.1       The XOR and EQV Functions of the XOR Gate       100         3.9.2       The XOR and EQV Functions of the EQV Gate       100         3.9.3       Multiple Gate Realizations of the XOR and EQV Functions       101         3.9.4       The Effect of Active Low Inputs to the XOR and EQV Functions       102         3.9.5       Summary of Conjugate Logic Circuit Symbols for XOR and EQV Gates       103         3.9.6       Controlled Logic Level Conversion       103         3.9.7       Construction and Waveform Analysis of Logic Circuit Symbols       102         3.10.1       NOT, AND, and OR Laws       106         3.10.2 <t< td=""><td></td><td>3.6</td><td></td><td></td><td>87</td></t<>                |    | 3.6   |           |                                                                    | 87  |  |

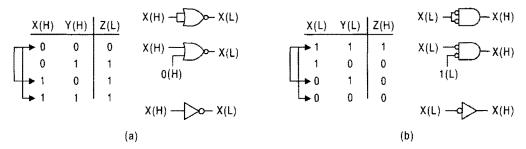

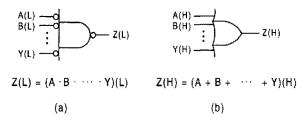

| 3.6.3       NOR Gate Realization of Logic AND and OR       89         3.6.4       NAND and NOR Gate Realization of Logic Level Conversion       90         3.6.5       The AND and OR       92         3.6.6       Summary of Logic Circuit Symbols for the AND and OR Functions<br>and Logic Level Conversion       94         3.7       Logic Level Incompatibility: Complementation       95         3.8       Reading and Construction of Mixed-Logic Circuit Symbology       98         3.9.1       The XOR and EQV Functions of the XOR Gate       100         3.9.2       The XOR and EQV Functions of the XOR and EQV Functions       101         3.9.4       The Effect of Active Low Inputs to the XOR and EQV Circuit Symbols       102         3.9.5       Summary of Conjugate Logic Circuit Symbols for XOR and EQV Gates       103         3.9.6       Construction and Waveform Analysis of Logic Circuit Symbols       102         3.9.7       Construction and Waveform Analysis of Logic Circuits Containing<br>XOR-Type Functions       104         3.10.1       NOT, AND, and OR Laws       106         3.10.2       The Concept of Duality       107         3.10.3       Associative, Commutative, Distributive, Absorptive, and<br>Consensus Laws       108         3.10.4       DeMorgan's Laws       110         3.11.1       Two Ste                                                                    |    |       | 3.6.1     | Logic Circuit Symbology for AND and OR                             | 87  |  |

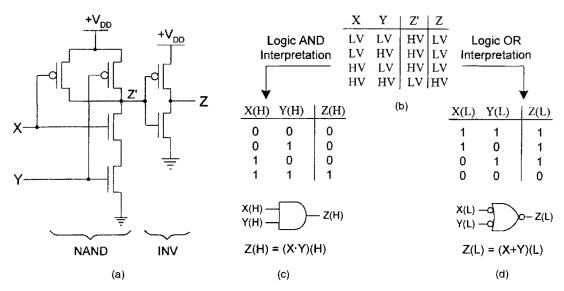

| 3.6.4       NAND and NOR Gate Realization of Logic Level Conversion       90         3.6.5       The AND and OR       92         3.6.6       Summary of Logic Circuit Symbols for the AND and OR Functions and Logic Level Conversion       94         3.7       Logic Level Incompatibility: Complementation       95         3.8       Reading and Construction of Mixed-Logic Circuits       97         3.9       XOR and EQV Operators and Their Mixed-Logic Circuit Symbology       98         3.9.1       The XOR and EQV Functions of the XOR Gate       100         3.9.2       The XOR and EQV Functions of the XOR and EQV Circuit Symbols       102         3.9.3       Multiple Gate Realizations of the XOR and EQV Functions       101         3.9.4       The Effect of Active Low Inputs to the XOR and EQV Gates       103         3.9.5       Summary of Conjugate Logic Circuit Symbols for XOR and EQV Gates       103         3.9.6       Controlled Logic Level Conversion       104         3.10.1       NOT, AND, and OR Laws       106         3.10.2       The Concept of Duality       107         3.10.3       Associative, Commutative, Distributive, Absorptive, and Consensus Laws       108         3.10.4       DeMorgan's Laws       110         3.11       Sumary of Useful Identities       111                                                                                                |    |       | 3.6.2     | NAND Gate Realization of Logic AND and OR                          | 88  |  |

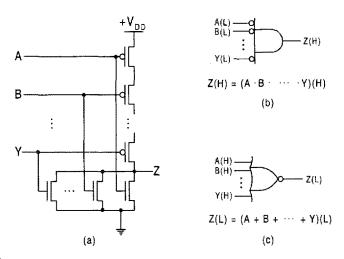

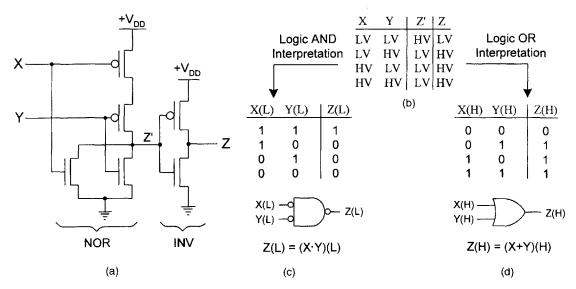

| 3.6.5       The AND and OR       92         3.6.6       Summary of Logic Circuit Symbols for the AND and OR Functions and Logic Level Conversion       94         3.7       Logie Level Incompatibility: Complementation       95         3.8       Reading and Construction of Mixed-Logic Circuits       97         3.9       XOR and EQV Operators and Their Mixed-Logic Circuit Symbology       98         3.9.1       The XOR and EQV Functions of the XOR Gate       100         3.9.2       The XOR and EQV Functions of the XOR and EQV Functions       101         3.9.4       The Effect of Active Low Inputs to the XOR and EQV Functions       102         3.9.5       Summary of Conjugate Logic Circuit Symbols for XOR and EQV Gates       103         3.9.6       Controlled Logic Level Conversion       103         3.9.7       Construction and Waveform Analysis of Logic Circuits Containing XOR-Type Functions       104         3.10.1       NOT, AND, and OR Laws       106         3.10.2       The Concept of Duality       107         3.10.3       Associative, Commutative, Distributive, Absorptive, and Consensus Laws       108         3.10.4       DeMorgan's Laws       110         3.11.1       Two Useful Corollaries       114         3.11.2       Summary of Useful Identities       115 <td></td> <td>3.6.3</td> <td>NOR Gate Realization of Logic AND and OR</td> <td>89</td>            |    |       | 3.6.3     | NOR Gate Realization of Logic AND and OR                           | 89  |  |

| AND and OR       92         3.6.6       Summary of Logic Circuit Symbols for the AND and OR Functions<br>and Logic Level Conversion       94         3.7       Logic Level Incompatibility: Complementation       95         3.8       Reading and Construction of Mixed-Logic Circuit Symbology       98         3.91       The XOR and EQV Functions of the XOR Gate       100         3.9.2       The XOR and EQV Functions of the ZOR and EQV Functions       101         3.9.4       The Effect of Active Low Inputs to the XOR and EQV Gates       103         3.9.5       Summary of Conjugate Logic Circuit Symbols for XOR and EQV Gates       103         3.9.6       Controlled Logic Level Conversion       103         3.9.7       Construction and Waveform Analysis of Logic Circuits Containing<br>XOR-Type Functions       104         3.10       Laws of Boolean Algebra       105         3.10.1       NOT, AND, and OR Laws       106         3.10.2       The Concept of Duality       107         3.10.3       Associative, Commutative, Distributive, Absorptive, and<br>Consensus Laws       110         3.1.1       Iwo Skel Examples       116         Further Reading       120       120         Problems       121       111         4.1       Introduction       131                                                                                                                                 |    |       | 3.6.4     | NAND and NOR Gate Realization of Logic Level Conversion            | 90  |  |

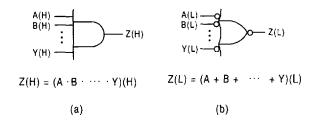

| 3.6.6       Summary of Logic Circuit Symbols for the AND and OR Functions<br>and Logic Level Conversion       94         3.7       Logic Level Incompatibility: Complementation       95         3.8       Reading and Construction of Mixed-Logic Circuits       97         3.9       XOR and EQV Operators and Their Mixed-Logic Circuit Symbology       98         3.9.1       The XOR and EQV Functions of the XOR Gate       100         3.9.2       The XOR and EQV Functions of the XOR and EQV Functions       101         3.9.4       The Effect of Active Low Inputs to the XOR and EQV Circuit Symbols       102         3.9.5       Summary of Conjugate Logic Circuit Symbols for XOR and EQV Gates       103         3.9.6       Controlled Logic Level Conversion       101         3.9.7       Construction and Waveform Analysis of Logic Circuits Containing<br>XOR-Type Functions       104         3.10       Laws of Boolean Algebra       105         3.10.1       NOT, AND, and OR Laws       106         3.10.2       The Concept of Duality       107         3.10.3       Associative, Commutative, Distributive, Absorptive, and<br>Consensus Laws       110         3.11.1       Laws of XOR Algebra       111         3.11.1       Summary of Useful Identities       115         3.12.1       Worked Examples       116<                                                                             |    |       | 3.6.5     | The AND and OR Gates and Their Realization of Logic                |     |  |

| and Logic Level Conversion943.7Logic Level Incompatibility: Complementation953.8Reading and Construction of Mixed-Logic Circuits973.9XOR and EQV Operators and Their Mixed-Logic Circuit Symbology983.9.1The XOR and EQV Functions of the XOR Gate1003.9.2The XOR and EQV Functions of the ZOR and EQV Functions1013.9.4The Effect of Active Low Inputs to the XOR and EQV Circuit Symbols1023.9.5Summary of Conjugate Logic Circuit Symbols for XOR and EQV Gates1033.9.6Controlled Logic Level Conversion1033.9.7Construction and Waveform Analysis of Logic Circuits Containing XOR-Type Functions1043.10Laws of Boolean Algebra1053.10.1NOT, AND, and OR Laws1063.10.2The Concept of Duality1073.10.3Associative, Commutative, Distributive, Absorptive, and Consensus Laws1103.11Laws of XOR Algebra1113.11.1Two Useful Corollaries1143.11.2Summary of Useful Identities1153.12Worked Examples116Further Reading120Problems1214.Logic Function Representation and Minimization1314.1Introduction1314.2.2The POS Representation1344.3Introduction to Logic Function Graphics1374.3.1First-Order K-maps1384.3.3Third-Order K-maps1384.3.3Third-Order                                                                                                                                                                                                                                                                            |    |       |           | AND and OR                                                         | 92  |  |

| 3.7       Logic Level Incompatibility: Complementation       95         3.8       Reading and Construction of Mixed-Logic Circuits       97         3.9       XOR and EQV Operators and Their Mixed-Logic Circuit Symbology       98         3.9.1       The XOR and EQV Functions of the XOR Gate       100         3.9.2       The XOR and EQV Functions of the EQV Gate       100         3.9.3       Multiple Gate Realizations of the XOR and EQV Functions       101         3.9.4       The Effect of Active Low Inputs to the XOR and EQV Gates       103         3.9.5       Summary of Conjugate Logic Circuit Symbols for XOR and EQV Gates       103         3.9.6       Controlled Logic Level Conversion       103         3.9.7       Construction and Waveform Analysis of Logic Circuits Containing XOR-Type Functions       104         3.10       Laws of Boolean Algebra       105       105         3.10.1       NOT, AND, and OR Laws       106       102       107         3.10.2       The Concept of Duality       107       107       1103         3.10.4       DeMorgan's Laws       110       111       3.11.1       108       114       3.11.2       Summary of Useful Identities       115         3.12       Worked Examples       116       116       116 <t< td=""><td></td><td>3.6.6</td><td>Summary of Logic Circuit Symbols for the AND and OR Functions</td><td></td></t<>                    |    |       | 3.6.6     | Summary of Logic Circuit Symbols for the AND and OR Functions      |     |  |

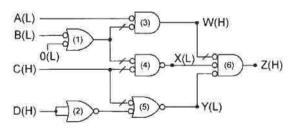

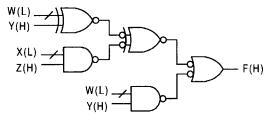

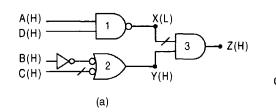

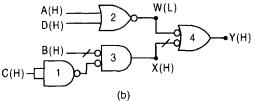

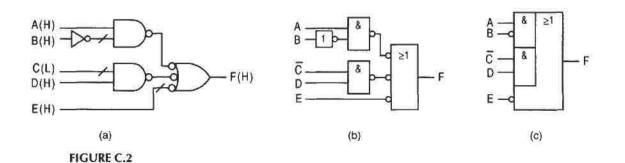

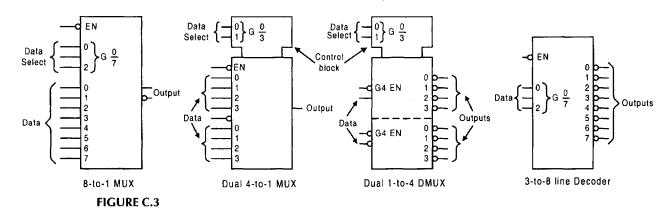

| 3.8       Reading and Construction of Mixed-Logic Circuits       97         3.9       XOR and EQV Operators and Their Mixed-Logic Circuit Symbology       98         3.9.1       The XOR and EQV Functions of the XOR Gate       100         3.9.2       The XOR and EQV Functions of the XOR and EQV Functions       101         3.9.3       Multiple Gate Realizations of the XOR and EQV Functions       101         3.9.4       The Effect of Active Low Inputs to the XOR and EQV Circuit Symbols       102         3.9.5       Summary of Conjugate Logic Circuit Symbols for XOR and EQV Gates       103         3.9.6       Construction and Waveform Analysis of Logic Circuits Containing XOR-Type Functions       104         3.10       Laws of Boolean Algebra       105       101         3.10.1       NOT, AND, and OR Laws       106       106         3.10.2       The Concept of Duality       107       3.10.3       Associative, Commutative, Distributive, Absorptive, and Consensus Laws       110         3.10.4       DeMorgan's Laws       116       111       3.11.2       Summary of Useful Identities       115         3.12       Worked Examples       116       116       116       116       120         Problems       121       Vorked Examples       131       131       131       13                                                                                                           |    |       |           | and Logic Level Conversion                                         | 94  |  |

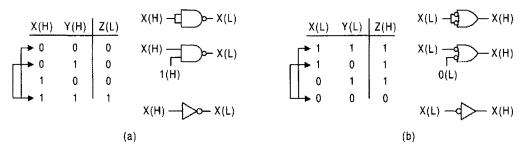

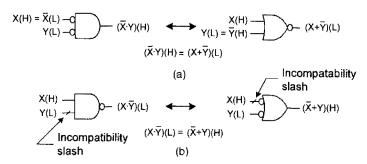

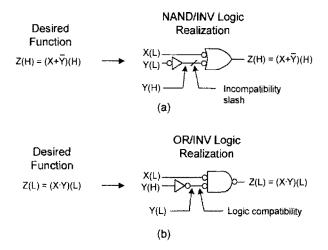

| 3.9       XOR and EQV Operators and Their Mixed-Logic Circuit Symbology       98         3.9.1       The XOR and EQV Functions of the XOR Gate       100         3.9.2       The XOR and EQV Functions of the XOR Gate       100         3.9.3       Multiple Gate Realizations of the XOR and EQV Functions       101         3.9.4       The Effect of Active Low Inputs to the XOR and EQV Circuit Symbols       102         3.9.5       Summary of Conjugate Logic Circuit Symbols for XOR and EQV Gates       103         3.9.6       Controlled Logic Level Conversion       103         3.9.7       Construction and Waveform Analysis of Logic Circuits Containing XOR-Type Functions       104         3.10       Laws of Boolean Algebra       105         3.10.1       NOT, AND, and OR Laws       106         3.10.2       The Concept of Duality       107         3.10.3       Associative, Commutative, Distributive, Absorptive, and Consensus Laws       110         3.11       Laws of XOR Algebra       111         3.11.1       Two Useful Corollaries       114         3.11.2       Summary of Useful Identities       115         3.12       Worked Examples       116         Further Reading       120       120         Problems       121       131                                                                                                                                                     |    | 3.7   | Logic I   | Level Incompatibility: Complementation                             | 95  |  |

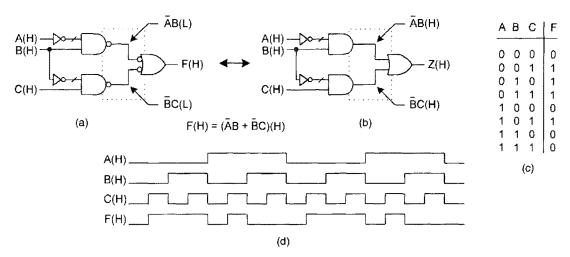

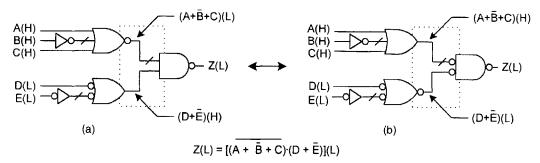

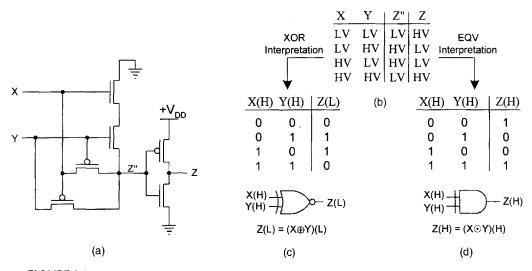

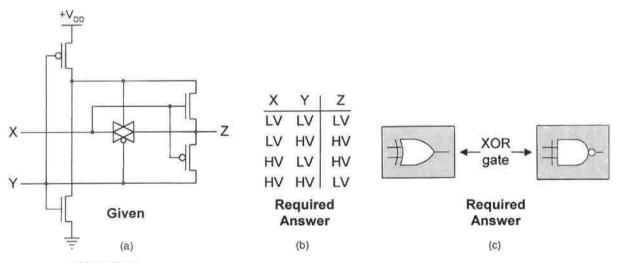

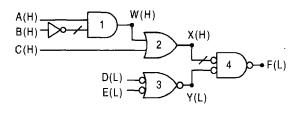

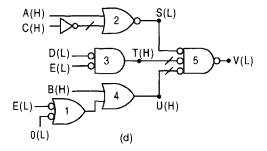

| 3.9.1       The XOR and EQV Functions of the XOR Gate       100         3.9.2       The XOR and EQV Functions of the EQV Gate       100         3.9.3       Multiple Gate Realizations of the XOR and EQV Functions       101         3.9.4       The Effect of Active Low Inputs to the XOR and EQV Circuit Symbols       102         3.9.5       Summary of Conjugate Logic Circuit Symbols for XOR and EQV Gates       103         3.9.6       Controlled Logic Level Conversion       103         3.9.7       Construction and Waveform Analysis of Logic Circuits Containing XOR-Type Functions       104         3.10       Laws of Boolean Algebra       105       105         3.10.1       NOT, AND, and OR Laws       106       107       3.10.3       Associative, Commutative, Distributive, Absorptive, and Consensus Laws       108         3.10.4       DeMorgan's Laws       110       111       3.11.1       Two Useful Corollaries       114         3.11.1       Two Useful Corollaries       114       3.11.2       Summary of Useful Identities       115         3.12       Worked Examples       116       Further Reading       120         Problems       121       131       4.2.1       The SOP Representation       131         4.2.2       The POS Representation       131       1                                                                                                                    |    | 3.8   | Readin    | g and Construction of Mixed-Logic Circuits                         | 97  |  |

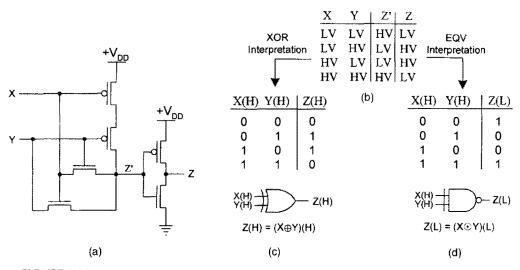

| 3.9.2       The XOR and EQV Functions of the EQV Gate       100         3.9.3       Multiple Gate Realizations of the XOR and EQV Functions       101         3.9.4       The Effect of Active Low Inputs to the XOR and EQV Circuit Symbols       102         3.9.5       Summary of Conjugate Logic Circuit Symbols for XOR and EQV Gates       103         3.9.6       Controlled Logic Level Conversion       103         3.9.7       Construction and Waveform Analysis of Logic Circuits Containing XOR-Type Functions       104         3.10       Laws of Boolean Algebra       105       105         3.10.1       NOT, AND, and OR Laws       106       107         3.10.2       The Concept of Duality       107       107         3.10.4       DeMorgan's Laws       108       101         3.10.4       DeMorgan's Laws       110       111         3.11.1       Two Useful Corollaries       114       111         3.11.2       Summary of Useful Identities       115       115         3.12       Worked Examples       116       116         Further Reading       120       121         4.       Logic Function Representation and Minimization       131       131         4.2       SOP and POS Forms       131       131                                                                                                                                                                                        |    | 3.9   | XOR a     | nd EQV Operators and Their Mixed-Logic Circuit Symbology           | 98  |  |

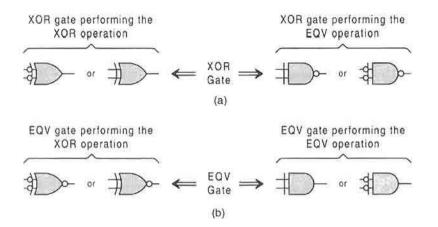

| 3.9.3       Multiple Gate Realizations of the XOR and EQV Functions       101         3.9.4       The Effect of Active Low Inputs to the XOR and EQV Circuit Symbols       102         3.9.5       Summary of Conjugate Logic Circuit Symbols for XOR and EQV Gates       103         3.9.6       Controlled Logic Level Conversion       103         3.9.7       Construction and Waveform Analysis of Logic Circuits Containing XOR-Type Functions       104         3.10       Laws of Boolean Algebra       105         3.10.1       NOT, AND, and OR Laws       106         3.10.2       The Concept of Duality       107         3.10.3       Associative, Commutative, Distributive, Absorptive, and Consensus Laws       108         3.10.4       DeMorgan's Laws       111         3.11       Two Useful Corollaries       114         3.12       Summary of Useful Identities       115         3.12       Worked Examples       116         Further Reading       120       120         Problems       121       131         4.1       Introduction       131         4.2       SOP and POS Forms       131         4.2.1       The SOP Representation       131         4.2.2       The POS Representation       131      <                                                                                                                                                                                            |    |       | 3.9.1     | The XOR and EQV Functions of the XOR Gate                          | 100 |  |

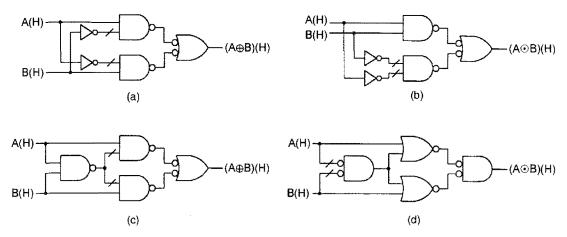

| 3.9.4       The Effect of Active Low Inputs to the XOR and EQV Circuit Symbols       102         3.9.5       Summary of Conjugate Logic Circuit Symbols for XOR and EQV Gates       103         3.9.6       Controlled Logic Level Conversion       103         3.9.7       Construction and Waveform Analysis of Logic Circuits Containing XOR-Type Functions       104         3.10       Laws of Boolean Algebra       105         3.10.1       NOT, AND, and OR Laws       106         3.10.2       The Concept of Duality       107         3.10.3       Associative, Commutative, Distributive, Absorptive, and Consensus Laws       108         3.10.4       DeMorgan's Laws       110         3.11       Laws of XOR Algebra       111         3.11.1       Two Useful Corollaries       114         3.11.2       Summary of Useful Identities       115         3.12       Worked Examples       116         Further Reading       120         Problems       121         4.       Logic Function Representation and Minimization       131         4.1       Introduction       131         4.2       SOP and POS Forms       131         4.2.1       The SOP Representation       131         4.2.2       The POS Represe                                                                                                                                                                                               |    |       | 3.9.2     | The XOR and EQV Functions of the EQV Gate                          | 100 |  |

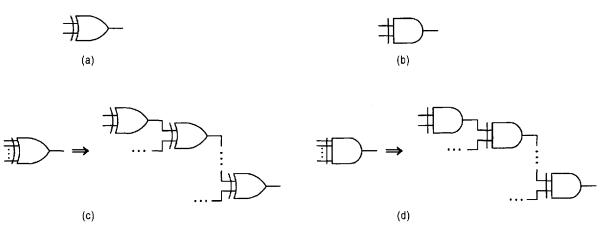

| 3.9.5       Summary of Conjugate Logic Circuit Symbols for XOR and EQV Gates       103         3.9.6       Controlled Logic Level Conversion       103         3.9.7       Construction and Waveform Analysis of Logic Circuits Containing XOR-Type Functions       104         3.10       Laws of Boolean Algebra       105         3.10.1       NOT, AND, and OR Laws       106         3.10.2       The Concept of Duality       107         3.10.3       Associative, Commutative, Distributive, Absorptive, and Consensus Laws       108         3.10.4       DeMorgan's Laws       110         3.11       Laws of XOR Algebra       111         3.11.1       Two Useful Corollaries       114         3.11.2       Summary of Useful Identities       115         3.12       Worked Examples       116         Further Reading       120       120         Problems       121       131         4.1       Introduction       131         4.2       SOP and POS Forms       131         4.2.1       The SOP Representation       131         4.2.2       The POS Representation       131         4.3       Introduction to Logic Function Graphics       137         4.3.1       First-Order K-maps                                                                                                                                                                                                                          |    |       | 3.9.3     | Multiple Gate Realizations of the XOR and EQV Functions            | 101 |  |

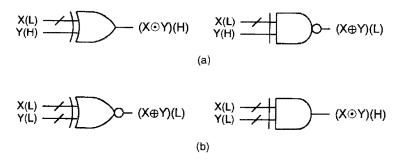

| 3.9.6Controlled Logic Level Conversion1033.9.7Construction and Waveform Analysis of Logic Circuits Containing<br>XOR-Type Functions1043.10Laws of Boolean Algebra1053.10.1NOT, AND, and OR Laws1063.10.2The Concept of Duality1073.10.3Associative, Commutative, Distributive, Absorptive, and<br>Consensus Laws1083.10.4DeMorgan's Laws1103.11Laws of XOR Algebra1113.11.1Two Useful Corollaries1143.11.2Summary of Useful Identities1153.12Worked Examples116Further Reading120Problems1214.Logic Function Representation and Minimization1314.1Introduction1314.2.1The SOP Representation1344.3Introduction to Logic Function Graphics1374.3.1First-Order K-maps1384.3.2Second-Order K-maps1384.3.3Third-Order K-maps140                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |    |       | 3.9.4     | The Effect of Active Low Inputs to the XOR and EQV Circuit Symbols | 102 |  |

| 3.9.7       Construction and Waveform Analysis of Logic Circuits Containing XOR-Type Functions       104         3.10       Laws of Boolean Algebra       105         3.10.1       NOT, AND, and OR Laws       106         3.10.2       The Concept of Duality       107         3.10.3       Associative, Commutative, Distributive, Absorptive, and Consensus Laws       108         3.10.4       DeMorgan's Laws       108         3.10.4       DeMorgan's Laws       110         3.11       Laws of XOR Algebra       111         3.11.2       Summary of Useful Identities       115         3.12       Worked Examples       116         Further Reading       120       120         Problems       121       131         4.1       Introduction       131         4.2       SOP and POS Forms       131         4.2.1       The SOP Representation       131         4.2.2       The POS Representation       134         4.3       Introduction to Logic Function Graphics       137         4.3.1       First-Order K-maps       138         4.3.2       Second-Order K-maps       138         4.3.3       Third-Order K-maps       138                                                                                                                                                                                                                                                                                   |    |       | 3.9.5     | Summary of Conjugate Logic Circuit Symbols for XOR and EQV Gates   | 103 |  |

| XOR-Type Functions1043.10Laws of Boolean Algebra1053.10.1NOT, AND, and OR Laws1063.10.2The Concept of Duality1073.10.3Associative, Commutative, Distributive, Absorptive, and<br>Consensus Laws1083.10.4DeMorgan's Laws1083.10.4DeMorgan's Laws1103.11Laws of XOR Algebra1113.11.1Two Useful Corollaries1143.11.2Summary of Useful Identities1153.12Worked Examples116Further Reading120Problems1214.Logic Function Representation and Minimization1314.1Introduction1314.2The SOP Representation1314.3Introduction to Logic Function Graphics1374.3.1First-Order K-maps1384.3.2Second-Order K-maps1384.3.3Third-Order K-maps140                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |    |       | 3.9.6     | Controlled Logic Level Conversion                                  | 103 |  |

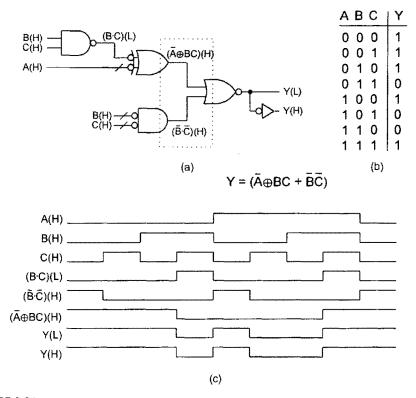

| 3.10Laws of Boolean Algebra1053.10.1NOT, AND, and OR Laws1063.10.2The Concept of Duality1073.10.3Associative, Commutative, Distributive, Absorptive, and<br>Consensus Laws1083.10.4DeMorgan's Laws1103.11Laws of XOR Algebra1113.11.1Two Useful Corollaries1143.11.2Summary of Useful Identities1153.12Worked Examples116Further Reading<br>Problems120Problems1214.Logic Function Representation and Minimization1314.1Introduction1314.2SOP and POS Forms1314.3Introduction to Logic Function Graphics1374.3.1First-Order K-maps1384.3.2Second-Order K-maps1384.3.3Third-Order K-maps140                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |    |       | 3.9.7     | Construction and Waveform Analysis of Logic Circuits Containing    |     |  |

| 3.10.1NOT, AND, and OR Laws1063.10.2The Concept of Duality1073.10.3Associative, Commutative, Distributive, Absorptive, and<br>Consensus Laws1083.10.4DeMorgan's Laws1103.11Laws of XOR Algebra1113.11.1Two Useful Corollaries1143.11.2Summary of Useful Identities1153.12Worked Examples116Further Reading120Problems1214.Logic Function Representation and Minimization1314.1Introduction1314.2SOP and POS Forms1314.2.1The SOP Representation1314.2.2The POS Representation1344.3Introduction to Logic Function Graphics1374.3.1First-Order K-maps1384.3.2Second-Order K-maps1384.3.3Third-Order K-maps140                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |    |       |           | XOR-Type Functions                                                 | 104 |  |

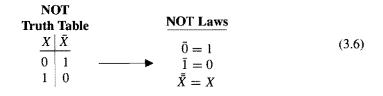

| 3.10.2The Concept of Duality1073.10.3Associative, Commutative, Distributive, Absorptive, and<br>Consensus Laws1083.10.4DeMorgan's Laws1103.11Laws of XOR Algebra1113.11.1Two Useful Corollaries1143.11.2Summary of Useful Identities1153.12Worked Examples116Further Reading120Problems1214.Logic Function Representation and Minimization1314.1Introduction1314.2SOP and POS Forms1314.2.1The SOP Representation1344.3Introduction to Logic Function Graphics1374.3.1First-Order K-maps1384.3.2Second-Order K-maps1384.3.3Third-Order K-maps140                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |    | 3.10  | Laws o    | f Boolean Algebra                                                  | 105 |  |

| 3.10.3       Associative, Commutative, Distributive, Absorptive, and         Consensus Laws       108         3.10.4       DeMorgan's Laws       110         3.11       Laws of XOR Algebra       111         3.11.1       Two Useful Corollaries       114         3.11.2       Summary of Useful Identities       115         3.12       Worked Examples       116         Further Reading       120         Problems       121         4.       Logic Function Representation and Minimization       131         4.1       Introduction       131         4.2       SOP and POS Forms       131         4.2.1       The SOP Representation       131         4.2.2       The POS Representation       131         4.3       Introduction to Logic Function Graphics       137         4.3.1       First-Order K-maps       138         4.3.2       Second-Order K-maps       138         4.3.3       Third-Order K-maps       140                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |    |       | 3.10.1    | NOT, AND, and OR Laws                                              | 106 |  |

| Consensus Laws1083.10.4DeMorgan's Laws1103.11Laws of XOR Algebra1113.11.1Two Useful Corollaries1143.11.2Summary of Useful Identities1153.12Worked Examples116Further Reading120Problems1214.Logic Function Representation and Minimization4.1Introduction1314.2SOP and POS Forms1314.2.1The SOP Representation1314.2.2The POS Representation1344.3Introduction to Logic Function Graphics1374.3.1First-Order K-maps1384.3.3Third-Order K-maps1384.3.3Third-Order K-maps140                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |    |       | 3.10.2    | The Concept of Duality                                             | 107 |  |

| 3.10.4DeMorgan's Laws1103.11Laws of XOR Algebra1113.11.1Two Useful Corollaries1143.11.2Summary of Useful Identities1153.12Worked Examples116Further Reading120Problems1214.Logic Function Representation and Minimization4.1Introduction1314.2SOP and POS Forms1314.2.1The SOP Representation1314.2.2The POS Representation1344.3Introduction to Logic Function Graphics1374.3.1First-Order K-maps1384.3.2Second-Order K-maps1384.3.3Third-Order K-maps140                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |    |       | 3.10.3    | Associative, Commutative, Distributive, Absorptive, and            |     |  |

| 3.11Laws of XOR Algebra1113.11.1Two Useful Corollaries1143.11.2Summary of Useful Identities1153.12Worked Examples116Further Reading120Problems1214.Logic Function Representation and Minimization1314.1Introduction1314.2SOP and POS Forms1314.2.1The SOP Representation1314.2.2The POS Representation1344.3Introduction to Logic Function Graphics1374.3.1First-Order K-maps1384.3.3Third-Order K-maps140                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |    |       |           | Consensus Laws                                                     | 108 |  |

| 3.11.1Two Useful Corollaries1143.11.2Summary of Useful Identities1153.12Worked Examples116Further Reading120Problems1214.Logic Function Representation and Minimization1314.1Introduction1314.2SOP and POS Forms1314.2.1The SOP Representation1314.2.2The POS Representation1344.3Introduction to Logic Function Graphics1374.3.1First-Order K-maps1384.3.3Third-Order K-maps140                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |    |       | 3.10.4    | DeMorgan's Laws                                                    | 110 |  |

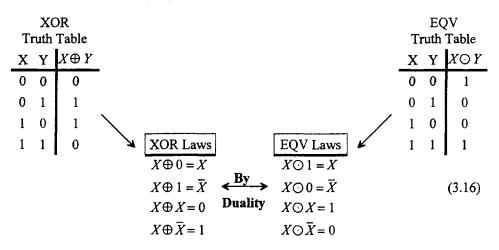

| 3.11.2Summary of Useful Identities1153.12Worked Examples116Further Reading120Problems1214.Logic Function Representation and Minimization1314.1Introduction1314.2SOP and POS Forms1314.2.1The SOP Representation1314.2.2The POS Representation1344.3Introduction to Logic Function Graphics1374.3.1First-Order K-maps1384.3.3Third-Order K-maps140                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |    | 3.11  | Laws o    | f XOR Algebra                                                      | 111 |  |

| 3.12Worked Examples116Further Reading120Problems1214.Logic Function Representation and Minimization1314.1Introduction1314.2SOP and POS Forms1314.2.1The SOP Representation1314.2.2The POS Representation1344.3Introduction to Logic Function Graphics1374.3.1First-Order K-maps1384.3.3Third-Order K-maps140                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |    |       | 3.11.1    | Two Useful Corollaries                                             | 114 |  |

| Further Reading<br>Problems120<br>1214. Logic Function Representation and Minimization1314.1Introduction1314.2SOP and POS Forms1314.2.1The SOP Representation1314.2.2The POS Representation1344.3Introduction to Logic Function Graphics1374.3.1First-Order K-maps1384.3.2Second-Order K-maps1384.3.3Third-Order K-maps140                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |    |       | 3.11.2    | Summary of Useful Identities                                       | 115 |  |

| Problems1214. Logic Function Representation and Minimization1314.1Introduction1314.2SOP and POS Forms1314.2.1The SOP Representation1314.2.2The POS Representation1344.3Introduction to Logic Function Graphics1374.3.1First-Order K-maps1384.3.2Second-Order K-maps1384.3.3Third-Order K-maps140                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |    | 3.12  | Worked    | d Examples                                                         | 116 |  |

| 4.Logic Function Representation and Minimization1314.1Introduction1314.2SOP and POS Forms1314.2.1The SOP Representation1314.2.2The POS Representation1344.3Introduction to Logic Function Graphics1374.3.1First-Order K-maps1384.3.2Second-Order K-maps1384.3.3Third-Order K-maps140                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |    |       | Further   | Reading                                                            | 120 |  |

| 4.1Introduction1314.2SOP and POS Forms1314.2.1The SOP Representation1314.2.2The POS Representation1344.3Introduction to Logic Function Graphics1374.3.1First-Order K-maps1384.3.2Second-Order K-maps1384.3.3Third-Order K-maps140                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |    |       | Problei   | ns                                                                 | 121 |  |

| 4.2SOP and POS Forms1314.2.1The SOP Representation1314.2.2The POS Representation1344.3Introduction to Logic Function Graphics1374.3.1First-Order K-maps1384.3.2Second-Order K-maps1384.3.3Third-Order K-maps140                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 4. | Logic | : Functio | on Representation and Minimization                                 | 131 |  |

| 4.2SOP and POS Forms1314.2.1The SOP Representation1314.2.2The POS Representation1344.3Introduction to Logic Function Graphics1374.3.1First-Order K-maps1384.3.2Second-Order K-maps1384.3.3Third-Order K-maps140                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |    | 4.1   | Introdu   | ction                                                              | 131 |  |

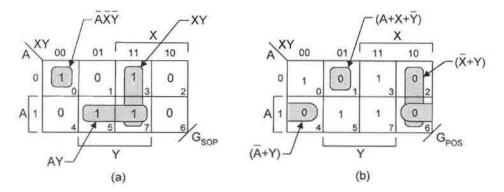

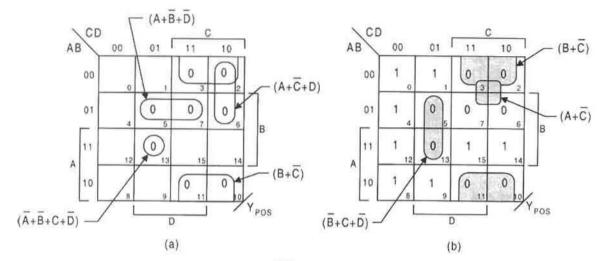

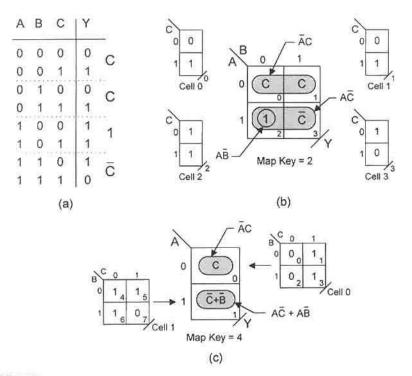

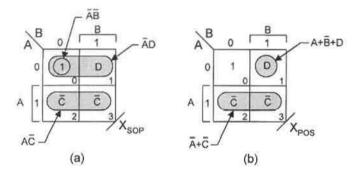

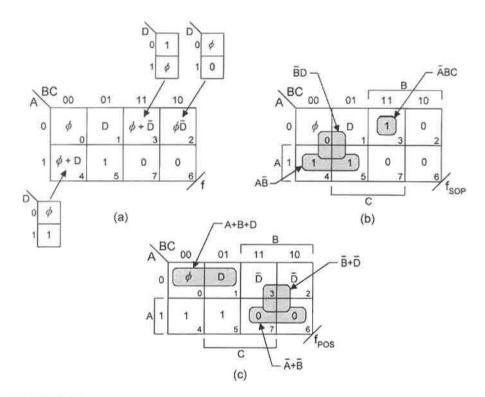

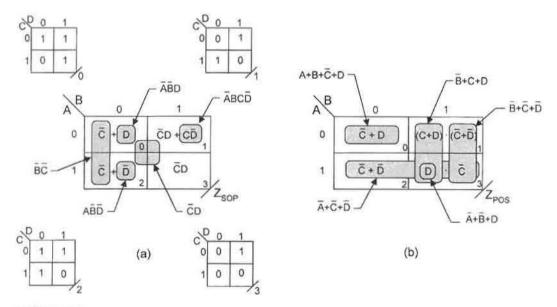

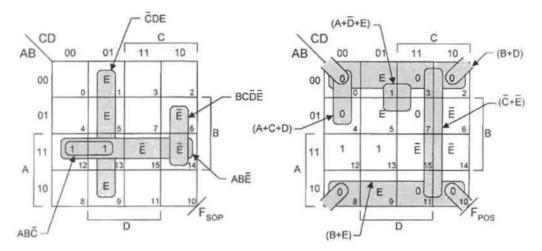

| 4.2.1The SOP Representation1314.2.2The POS Representation1344.3Introduction to Logic Function Graphics1374.3.1First-Order K-maps1384.3.2Second-Order K-maps1384.3.3Third-Order K-maps140                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |    |       |           |                                                                    |     |  |

| 4.2.2The POS Representation1344.3Introduction to Logic Function Graphics1374.3.1First-Order K-maps1384.3.2Second-Order K-maps1384.3.3Third-Order K-maps140                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |    |       |           |                                                                    |     |  |

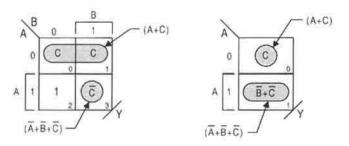

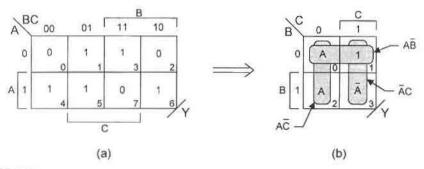

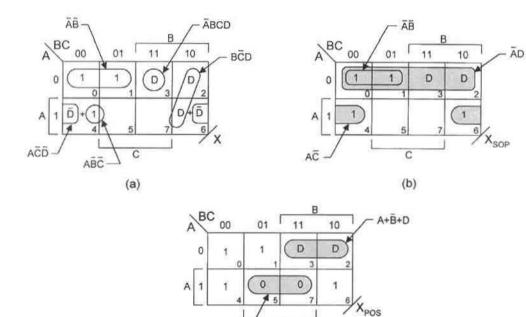

| 4.3Introduction to Logic Function Graphics1374.3.1First-Order K-maps1384.3.2Second-Order K-maps1384.3.3Third-Order K-maps140                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |    |       |           | •                                                                  |     |  |

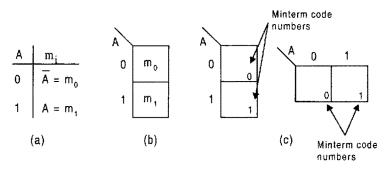

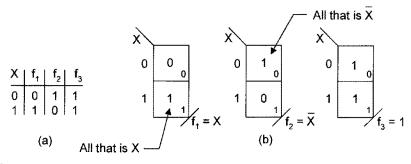

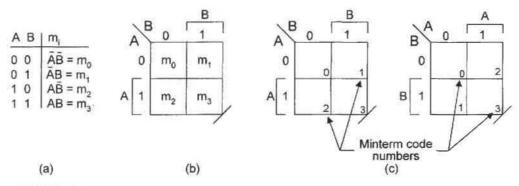

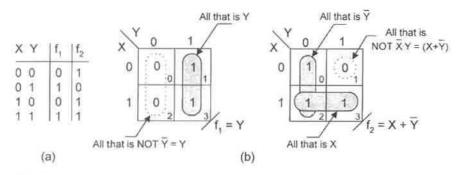

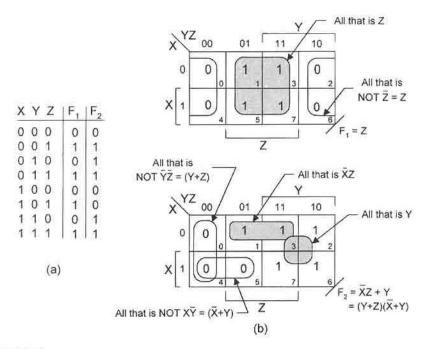

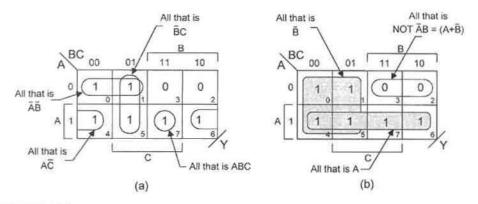

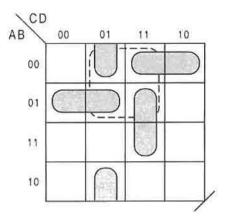

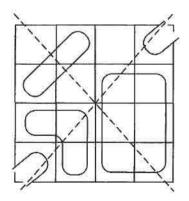

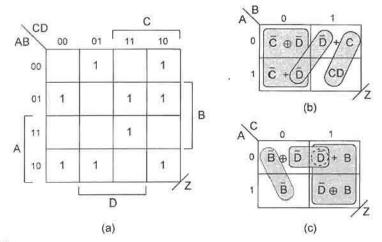

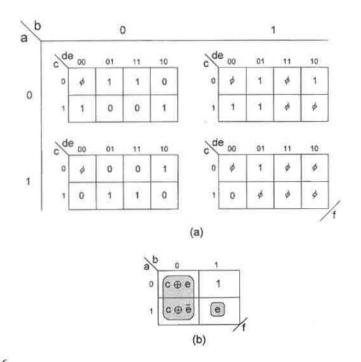

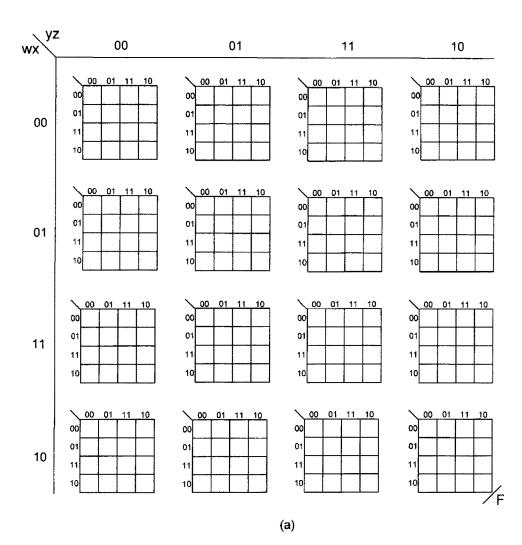

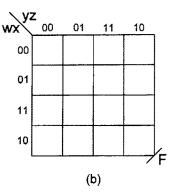

| 4.3.1       First-Order K-maps       138         4.3.2       Second-Order K-maps       138         4.3.3       Third-Order K-maps       140                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |    | 4.3   |           |                                                                    |     |  |

| 4.3.2Second-Order K-maps1384.3.3Third-Order K-maps140                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |    |       |           |                                                                    |     |  |

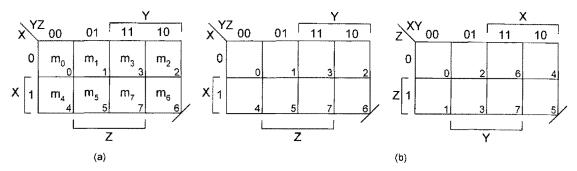

| 4.3.3 Third-Order K-maps 140                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |    |       |           |                                                                    |     |  |

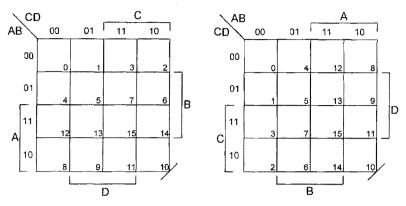

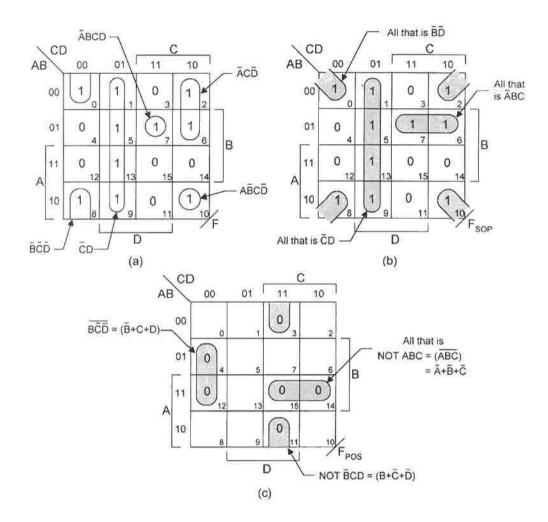

| I. I                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |    |       |           | •                                                                  |     |  |